一位全减器逻辑图

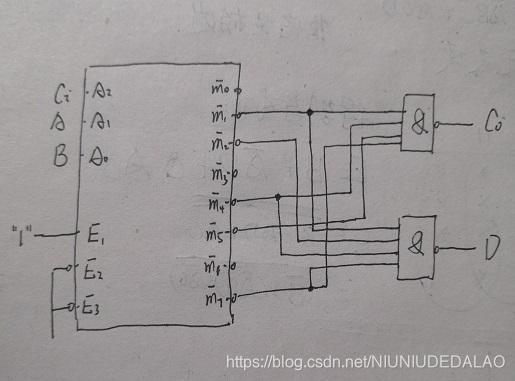

用74ls138实现一位全减器 - 数字电路图

图片尺寸547x219

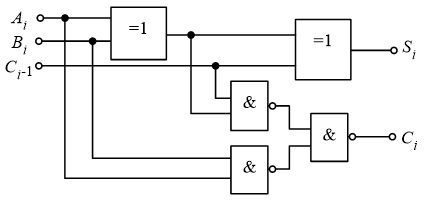

仿照全加器画出1位二进制数的全减器:输入被减数为a,减数为b,低位来的

图片尺寸530x570

这是38译码器设计的1位二进制全减器,输入为被减数,减数,和来自低位的

图片尺寸539x315

设计一个全减器电路

图片尺寸257x252

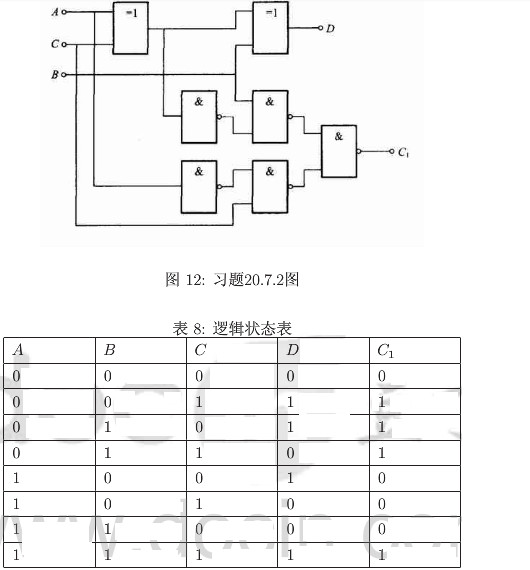

一位全减器逻辑电路图

图片尺寸500x216

用74ls138实现一位全减器 - 数字电路图

图片尺寸447x353

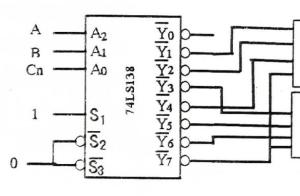

们分析一位全减器.

图片尺寸672x393

用74ls138和门电路设计1位二进制全减器

图片尺寸1190x1682

设计一1位全减器,a为被减数,b为减数,c为来自低位的信号,差为d,向高位

图片尺寸500x277

一位全加全减器地实现doc7页

图片尺寸792x1120

用vhdl结构描述设计一全减器

图片尺寸1080x810

用74ls138和门电路设计1位二进制全减器出错 真值表不符

图片尺寸1398x576![[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为.](https://i.ecywang.com/upload/1/img0.baidu.com/it/u=935994963,1782130575&fm=253&fmt=auto&app=138&f=JPEG?w=499&h=172)

[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为.

图片尺寸772x266

74ls138三线—八线译码器实现,逻辑图如下: 全减器

图片尺寸485x391

数字电路 全减器设计(最后结果与非式)

图片尺寸404x207

74ls138设计一位二进制全减器

图片尺寸515x381

如图所示电路可实现的逻辑功能是() - 上学吧找答案

图片尺寸426x202

multisim仿真我是新手,但是为什么我下面这个用译码器实现一位全减器

图片尺寸764x304

全减器

图片尺寸300x196

数字电路 全减器设计(最后结果与非式)

图片尺寸500x294

![[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为.](https://i.ecywang.com/upload/1/img0.baidu.com/it/u=935994963,1782130575&fm=253&fmt=auto&app=138&f=JPEG?w=499&h=172)

![[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为.](https://static.jiandati.com/d6da8de-chaoxing2016-1143650.jpeg)