一位全减器74153电路图

一位全减器逻辑电路图

图片尺寸500x216

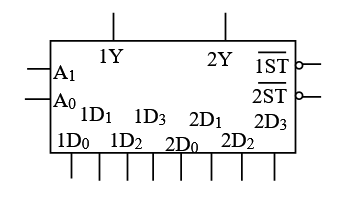

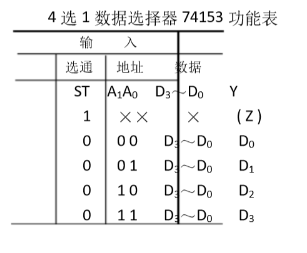

试用双4选1数据选择器74153设计一个全减器它能完成二进制减法运算s

图片尺寸356x199

三明学院数电期末复习题答案

图片尺寸625x389

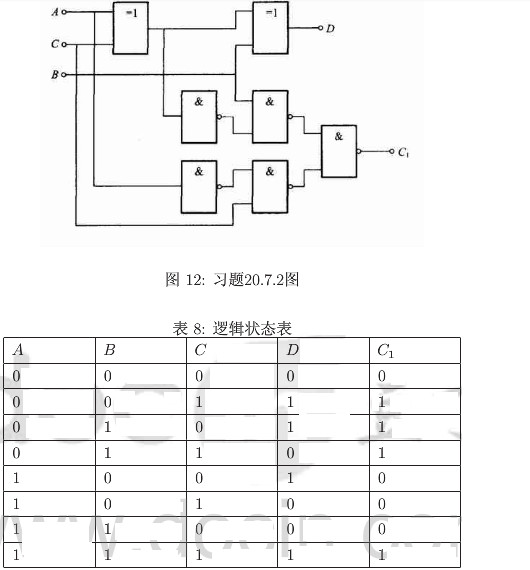

仿照全加器画出1位二进制数的全减器:输入被减数为a,减数为b,低位来的

图片尺寸530x570

5整体电路图

图片尺寸360x297

数字电路 全减器设计(最后结果与非式)

图片尺寸404x207

们分析一位全减器.

图片尺寸672x393

设计一个全减器电路

图片尺寸257x252

组合逻辑电路的分析方法和种类

图片尺寸2838x1542

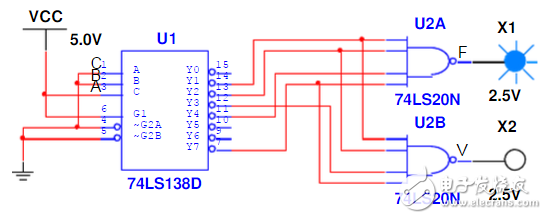

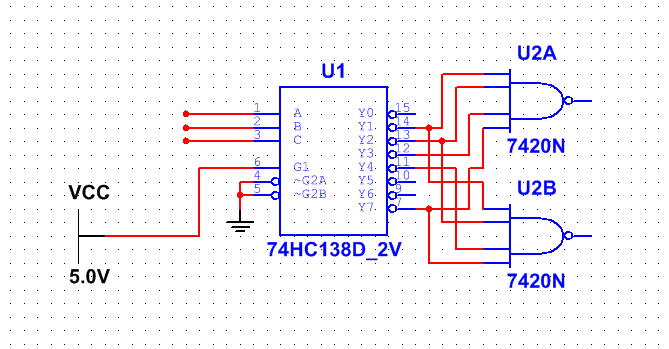

用74ls138和门电路设计1位二进制全减器出错 真值表不符

图片尺寸1398x576

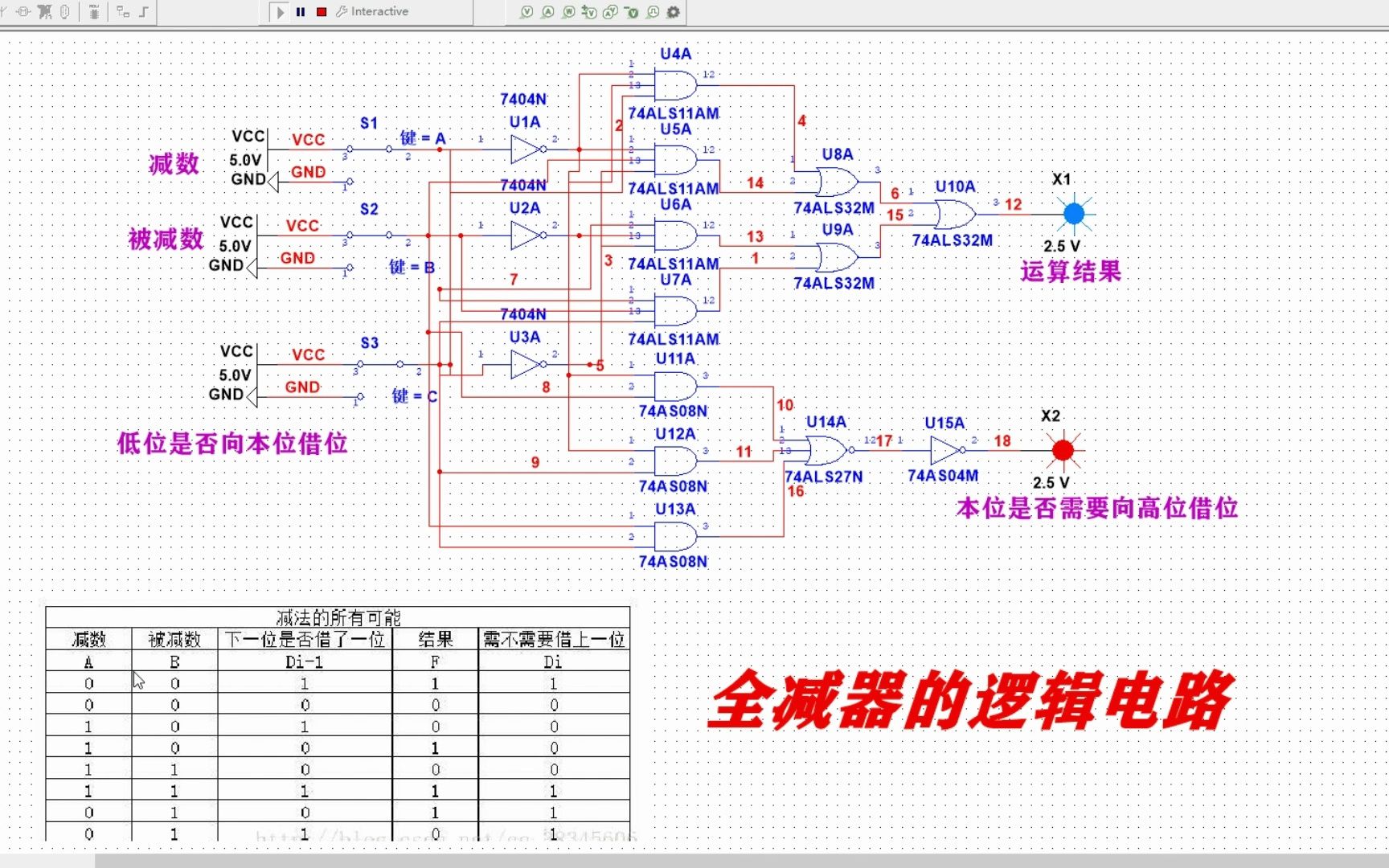

全减器的逻辑电路multisim仿真数电设计

图片尺寸1728x1080

试用双4选1数据选择器74153设计一个全减器它能完成二进制减法运算s

图片尺寸307x253![[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为.](https://i.ecywang.com/upload/1/img0.baidu.com/it/u=935994963,1782130575&fm=253&fmt=auto&app=138&f=JPEG?w=499&h=172)

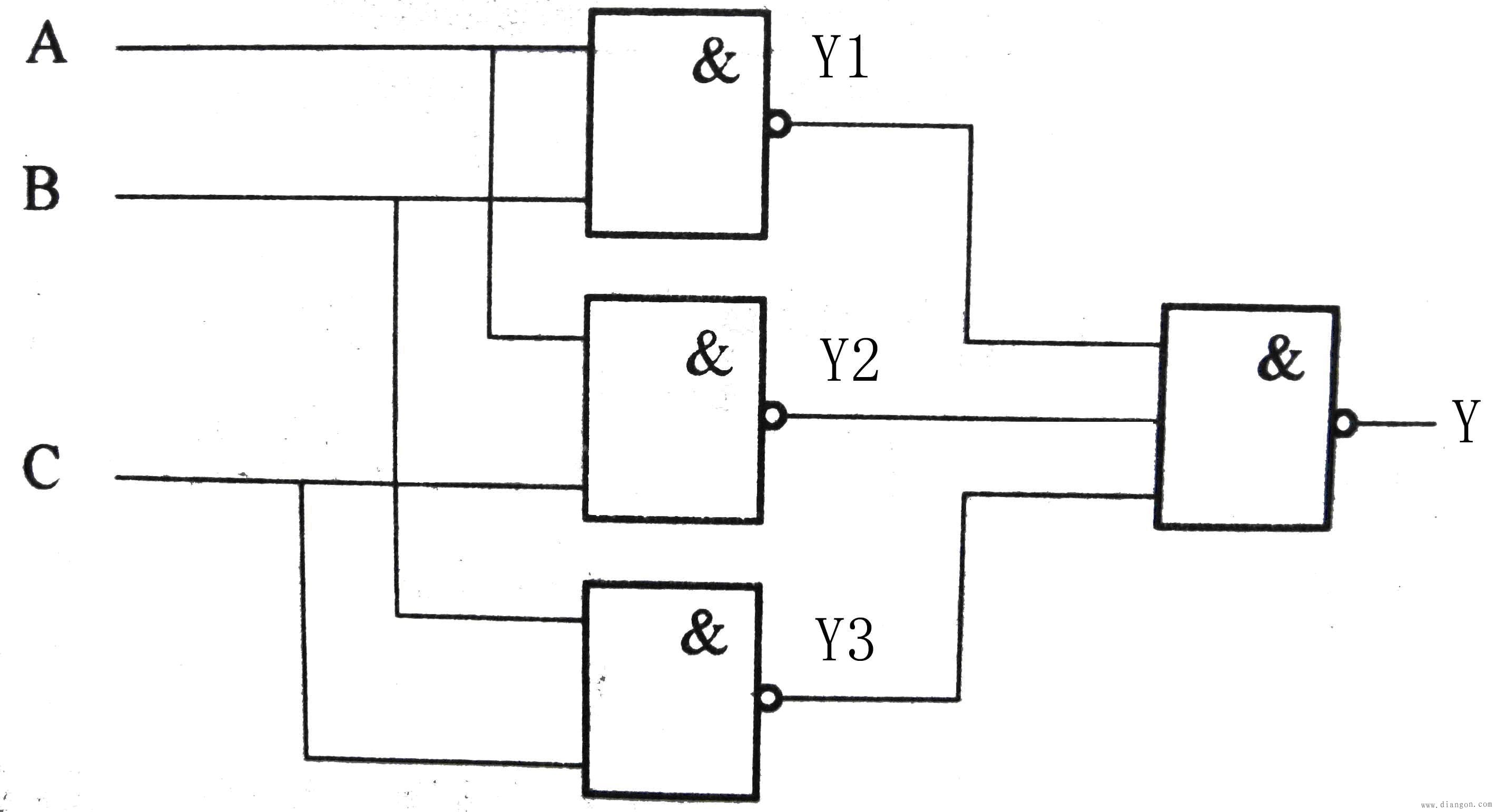

[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为.

图片尺寸772x266

设计一个一位全加减器,采用异或门和与非门来实现该电路 设一控制变量

图片尺寸1920x2560

用74ls138实现一位全减器

图片尺寸547x219

一位全加全减器地实现doc7页

图片尺寸792x1120

2,验证半加器,全加器的逻辑功能.

图片尺寸431x338

数字逻辑实验二组合逻辑电路

图片尺寸410x371

用vhdl结构描述设计一全减器

图片尺寸1080x810verilog实现减法器

图片尺寸669x349

猜你喜欢:利用74ls153设计全加器全减器全减器真值表74ls153全减器电路图一位全减器电路图74ls153全减器电路图设计一个全减器电路图74153一位全加器电路图74ls138做全减器电路图74ls153全加器电路图74153一位全加器接线图全减器逻辑电路图全减器门电路图一位全减器原理图74153电路图全减器电路设计74ls153电路图74153全加器图一位全减器逻辑图全减器原理图利用74ls153设计全减器一位全减器真值表一位全减器全减器逻辑图开关电源电路图及原理电路图讲解和实物图用与非门设计全减器电路图图解电路图阿圭罗白发图片朴彩英没有胸古人作揖手势图片潮流太空人壁纸奇葩说奇袭唐生与白骨精东莞镇街地图全图小女孩短发侧面小石子粘贴画怎么做孩子电视剧大全影视作品图片大全hermes戒指

![[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为.](https://static.jiandati.com/d6da8de-chaoxing2016-1143650.jpeg)