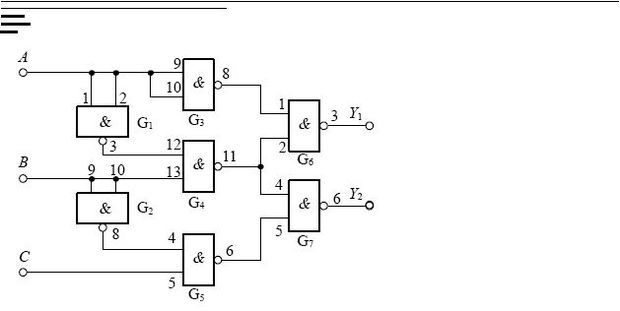

一位全加器逻辑电路图

电子/电路 一位全加器实验电路方法的研究 4 种门电路来实现,逻辑电路

图片尺寸353x226

全加器逻辑电路图

图片尺寸620x311

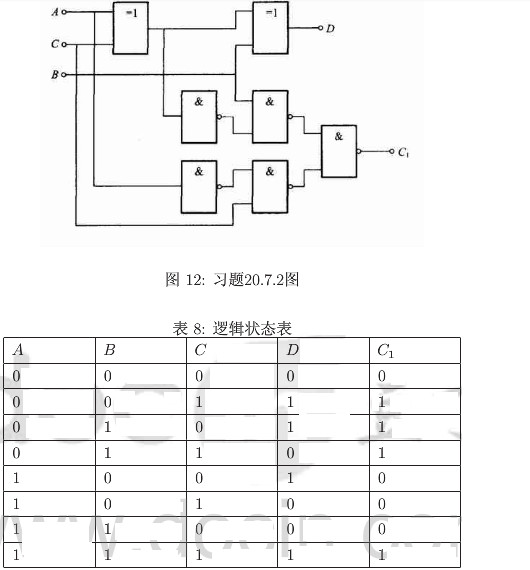

数字电路与逻辑设计:用74138实现一位全加器!

图片尺寸600x337

无忧文档 所有分类 工程科技 电子/电路 一位二进制全加器 号如图所示

图片尺寸554x328

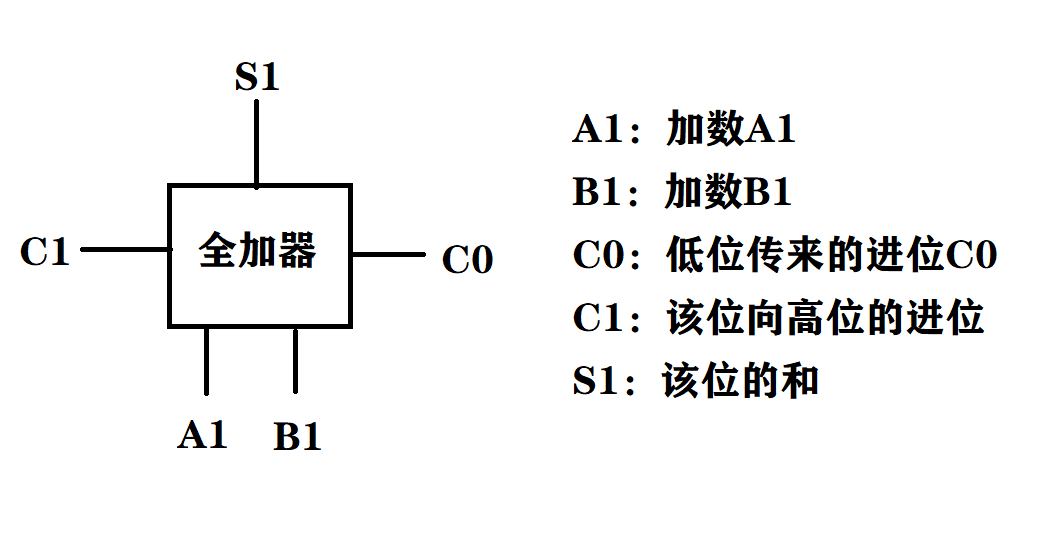

实用一位加法电路-全加器(全加器真值表,全加器的逻辑组合电路),几种

图片尺寸812x360

eda技术讲义 eda技术讲义 全 加 器 被加数,加数以及低位的进位三者

图片尺寸1080x810

54ls183 / 74ls183 lsttl型双进位保存全加器

图片尺寸431x338

课题名称组合逻辑全加器.

图片尺寸1820x1412用门电路设计一位的全加器

图片尺寸893x568

仿照全加器画出1位二进制数的全减器:输入被减数为a,减数为b,低位来的

图片尺寸530x570

74ls0074ls0874ls32全加器的ad原理图和pcb源文件

图片尺寸891x330

设计一个一位全加减器,采用异或门和与非门来实现该电路 设一控制变量

图片尺寸1920x2560

二进制全加器只涉及一位加法逻辑图和电路图

图片尺寸1044x555

背景技术:全加器是数字逻辑运算的基本单元,在数字集成电路系统中有

图片尺寸1000x727

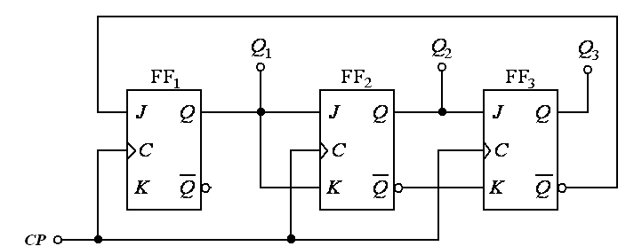

实验12: 组合逻辑电路-一位全加器

图片尺寸501x415

用74ls00,74ls86设计一个一位全加器电路

图片尺寸640x799

分析图1053所示逻辑电路图中为一位全加器试求1当a2a1a0110bb2b

图片尺寸630x251二进制全加器只涉及一位加法逻辑图和电路图

图片尺寸699x473

自制简单cup第三篇全加器

图片尺寸1003x506

华理数字逻辑实验二全加器

图片尺寸407x317

猜你喜欢:四位全加器一位全加器电路原理图全加器74ls74引脚图一位全加器真值表同或门逻辑符号全加器逻辑电路图一位全加器全加器电路图半加器逻辑电路图全减器逻辑电路图一位全加器原理图三人表决器逻辑电路图设计一个全减器电路图全加器电路逻辑电路图符号大全半加器电路图二位全加器原理图四位全加器原理图与非门逻辑电路图半加器电路图接线方法逻辑电路图八种逻辑门电路原理图74ls153全加器电路图三态门逻辑电路图全加器逻辑表达式异或门逻辑电路图逻辑电路图表达式全加器原理图全加器实验接线图动漫人体临摹宁静老公是谁淮阴区殷俊太平天国进军路线图莫兰迪色背景歌剧江江姐插曲百联南方购物中心壁纸人民币溜须拍马的图片文字闪光裂空座的图片麦克佐德的力量关关之猪