全加器的设计

实验一1位全加器设计.doc

图片尺寸792x1120

rtl基本知识:全加器设计(vhdl)

图片尺寸650x381

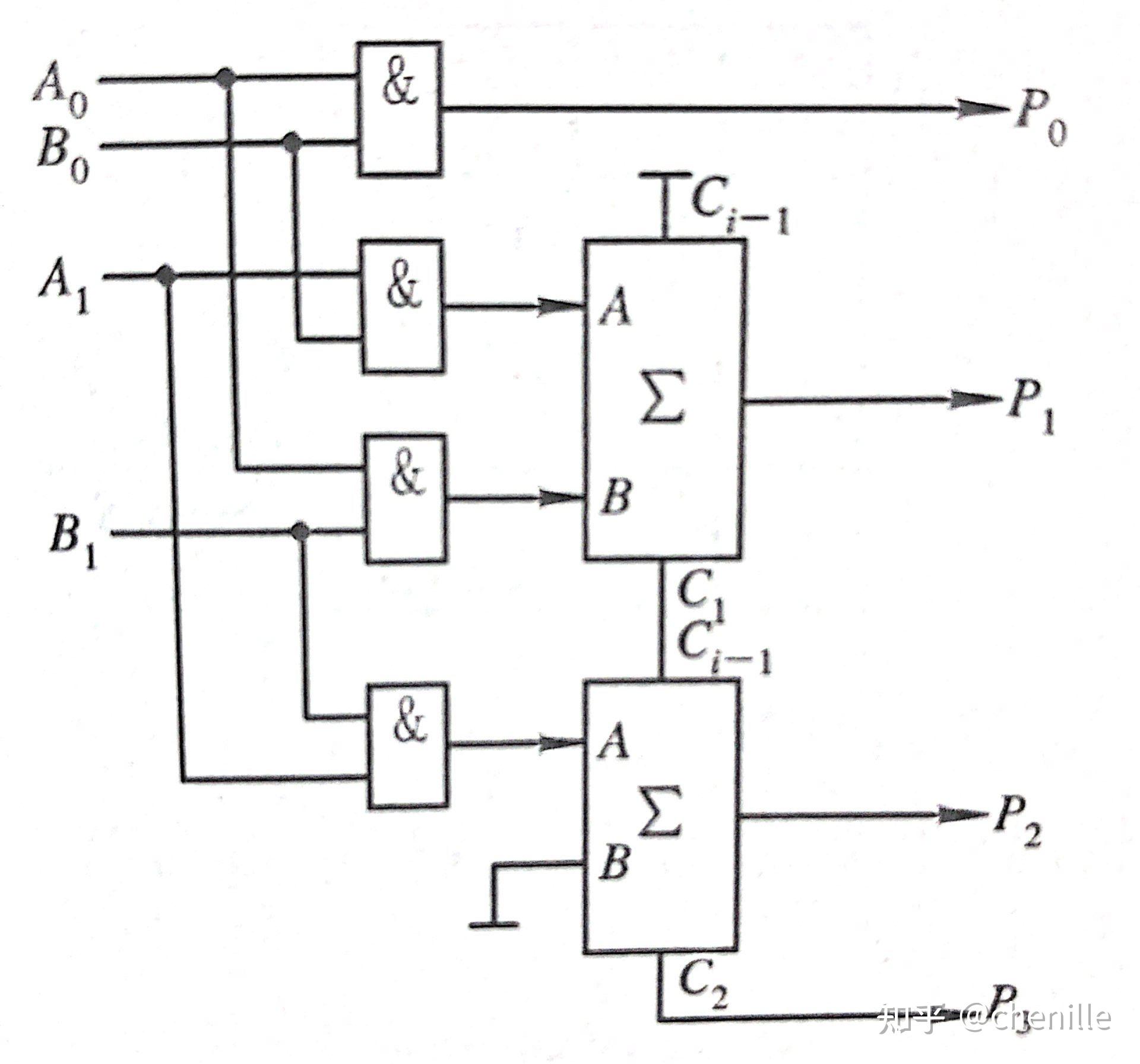

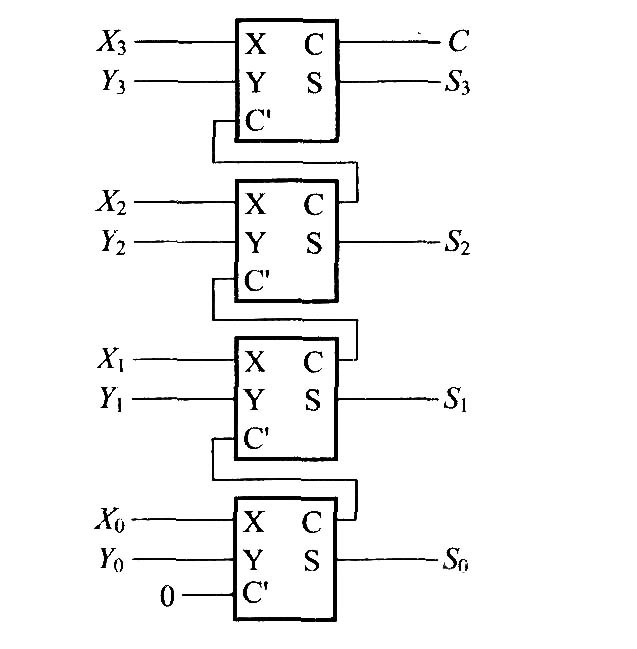

4位二进制全加器的设计

图片尺寸920x1302

数字电路设计1加法器

图片尺寸1920x1792

设计一个数字逻辑中的全加器,要求有实验原理,函数表达式,卡诺图,逻辑

图片尺寸279x224

四,设计全加器再次设置波形,运行,观察波形图出现0 warnings 说明编译

图片尺寸778x233

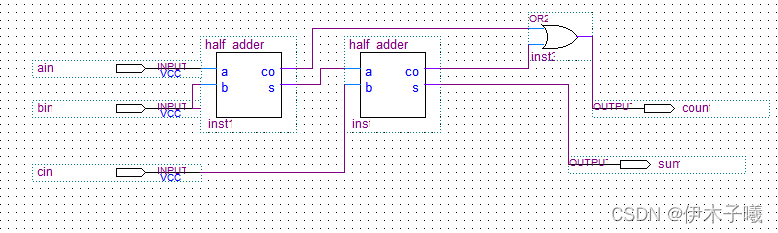

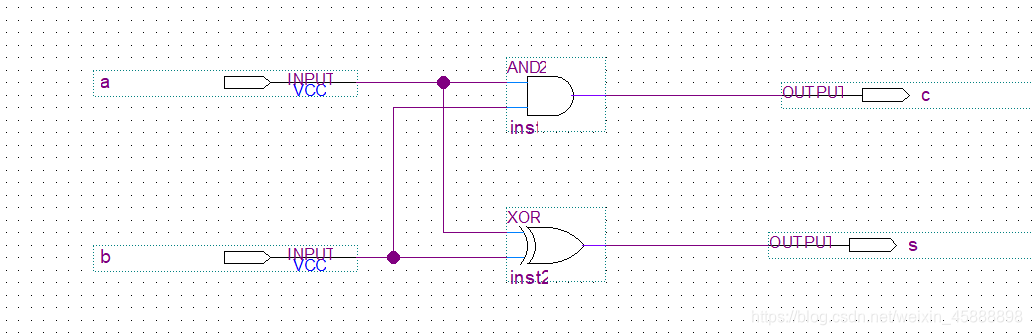

fpga设计入门--1位全加器的设计

图片尺寸1032x335

利用全加器构成3位加法计数器( 要有电路图的)

图片尺寸1488x525

logisim之4位全加器实现以及七段数码管显示_设计一个全加器,并用该全

图片尺寸2160x1440

quartusii1位全加器设计

图片尺寸1356x300

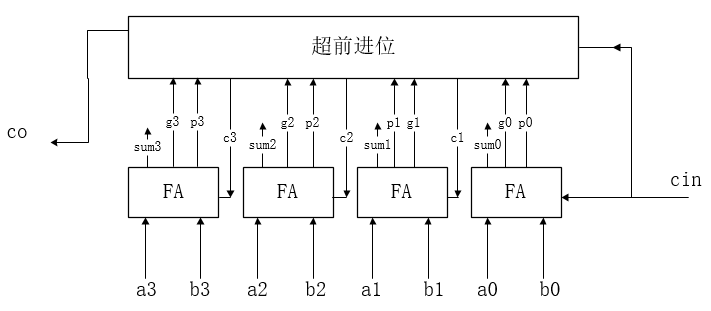

基于verilog hdl的超前进位全加器设计

图片尺寸711x311

设计8位全加器

图片尺寸970x620

用两片74ls138译码器设计一个全加器

图片尺寸920x1304

67一个全加器的整个设计包括三个模块,即底层两输入或门模块,半加器

图片尺寸888x500

使用全加器的4位加法运算电路

图片尺寸637x649

使用7455与或非门设计全加器quartusii软件仿真

图片尺寸1315x599

全加器设计

图片尺寸839x713

fpga一位全加器设计

图片尺寸581x263

实验一 一位二进制全加器设计

图片尺寸795x309

基于原理图的8位全加器层次化设计

图片尺寸816x235

猜你喜欢:全加器设计全加器设计图设计一位全加器全加器二位全加器一位全加器四位全加器设计全加器实验电路图全加器真值表两位全加器全加器原理图全加器电路全加器电路图全加器卡诺图一位全加器真值表四位全加器真值表二位全加器真值表一位全加器原理图四位全加器原理图二位全加器原理图一位全加器电路图利用74ls153设计全加器全加器实验接线图全加器逻辑电路图设计半加器实验电路图全加器逻辑表达式一位全加器电路原理图一位全加器逻辑电路图74ls153全加器电路图设计cqr250松鼠鳃角金龟纺织厂织布车间听歌卡通图片女孩多肉回声唐朝服装皇帝桐乡地铁获批新中式台灯必胜客的logo寓意爵士舞照片怎么摆姿势ac米兰高清壁纸 足球场福州高新区最新规划图