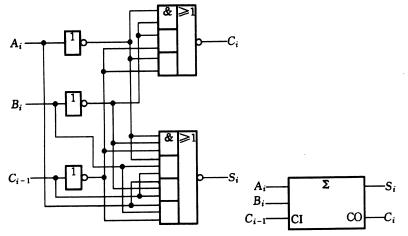

全加器设计

在verilog语言中使用门级建模设计一个由1位全加器组成的4位全加器

图片尺寸1435x808

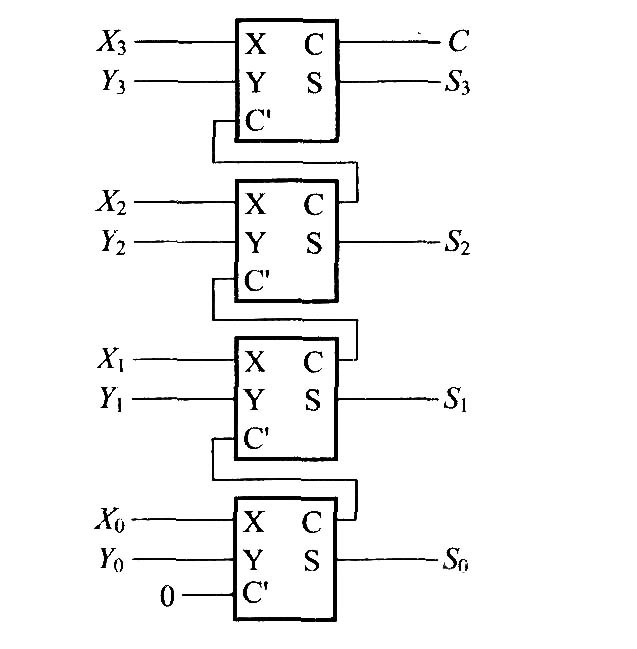

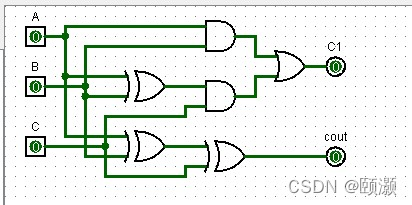

带超前进位的四位全加器

图片尺寸492x555

rtl基本知识:全加器设计(vhdl)

图片尺寸650x381

实验一1位全加器设计.doc

图片尺寸792x1120

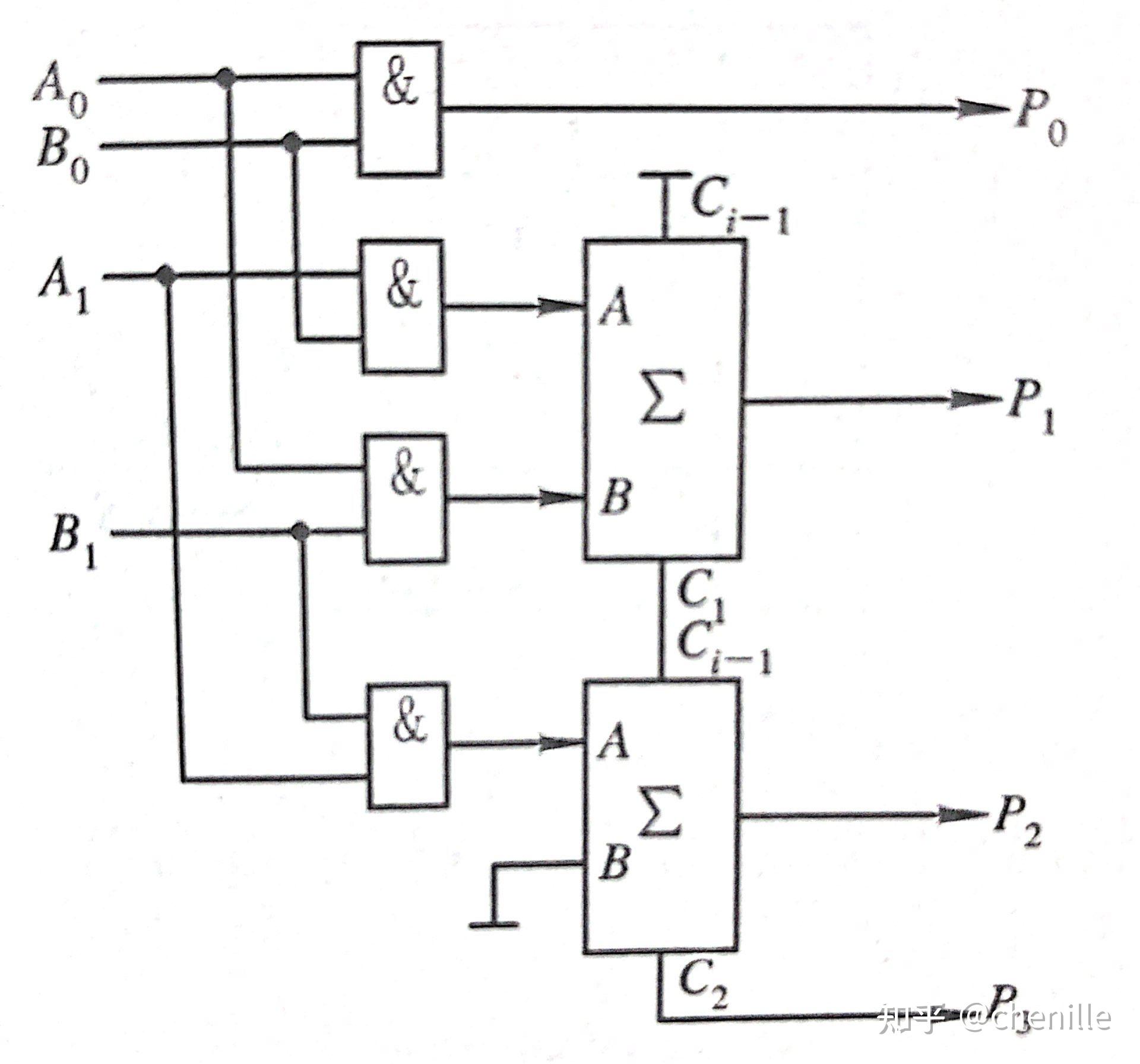

使用全加器的4位加法运算电路

图片尺寸637x649

求用两片74ls138设计一个全加器的电路图?

图片尺寸486x269

设计一个数字逻辑中的全加器,要求有实验原理,函数表达式,卡诺图,逻辑

图片尺寸279x224

数字电路设计1加法器

图片尺寸1920x1792

采用verilog hdl语言设计该4位全加器,通过主模块调用子模块(1位全加

图片尺寸362x367

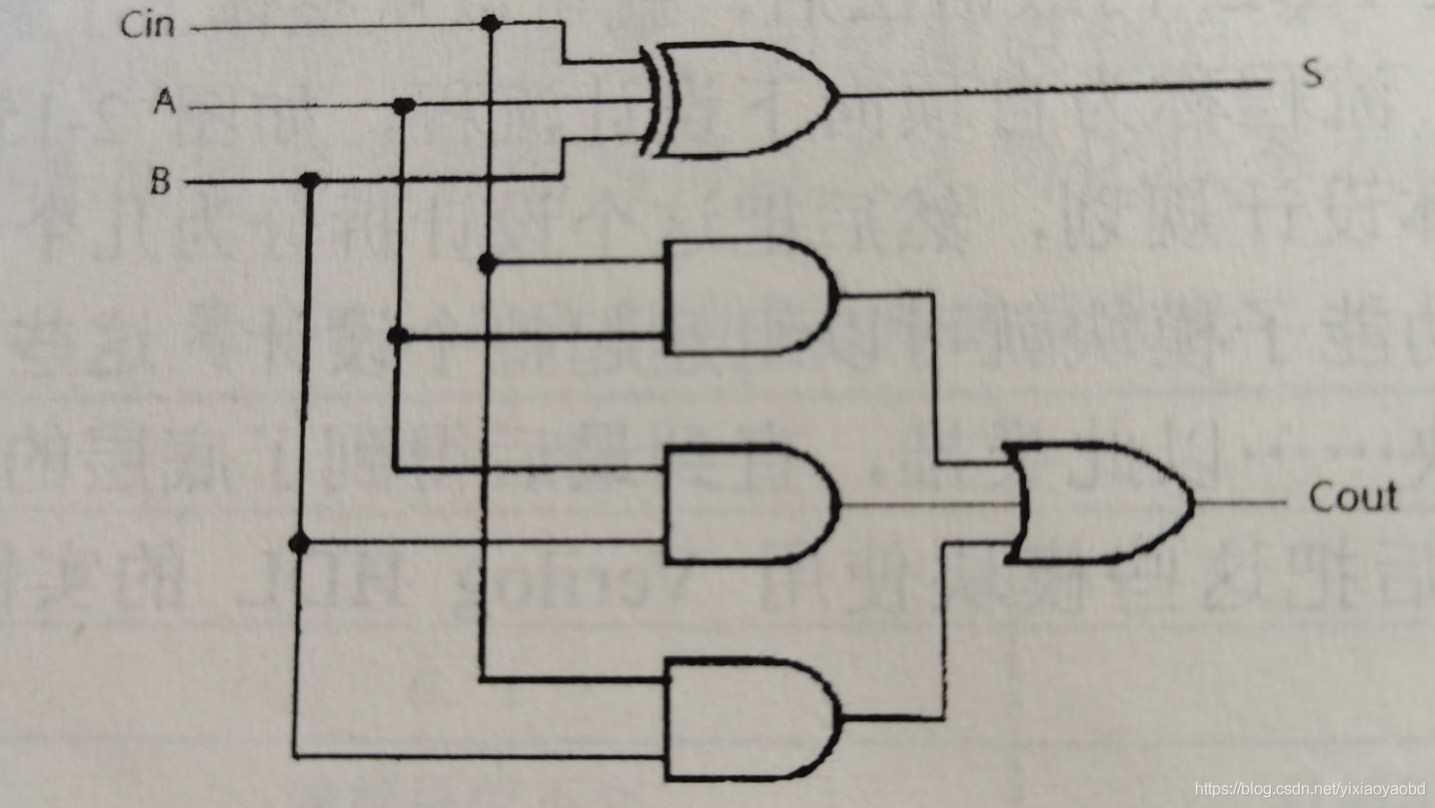

二进制全加器只涉及一位加法逻辑图和电路图

图片尺寸1044x555

设计8位全加器

图片尺寸970x620

4位二进制全加器的设计

图片尺寸920x1302

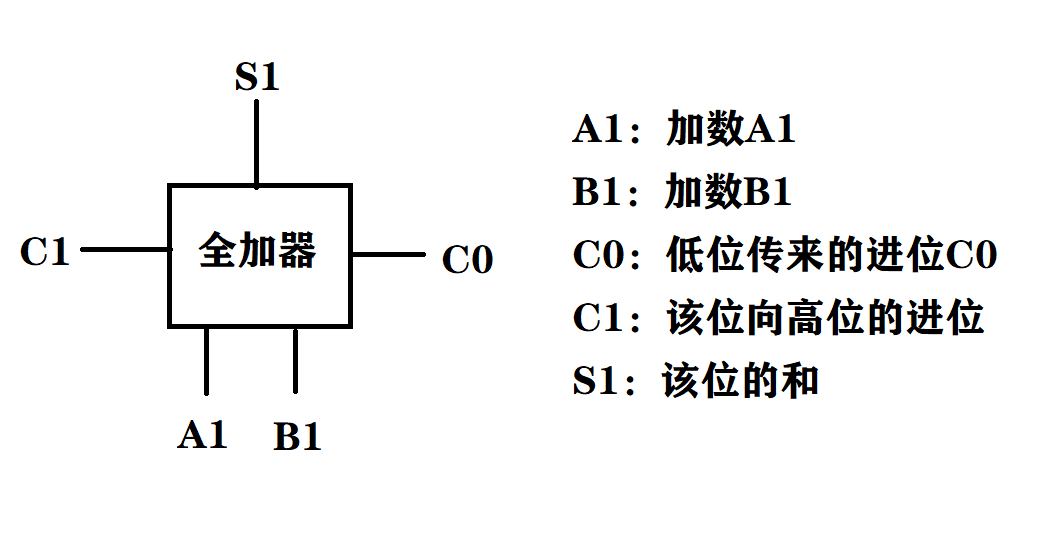

全加器

图片尺寸408x236

实验一 一位二进制全加器设计

图片尺寸795x309

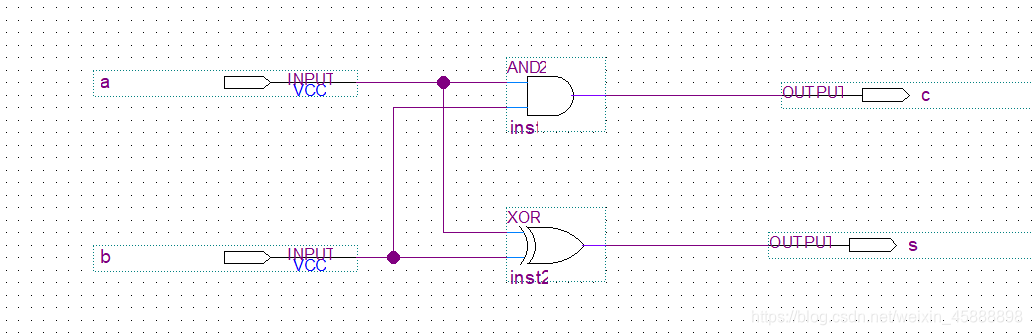

fpga设计入门--1位全加器的设计_全加器顶层文件-csdn博客

图片尺寸1032x335

基于原理图的8位全加器层次化设计

图片尺寸816x235

一种亚阈值抗噪声的全加器电路

图片尺寸903x1000

图1-1 全加器电路图

图片尺寸412x205

用原理图输入法设计四位全加器实验

图片尺寸800x1132

利用全加器构成3位加法计数器( 要有电路图的)

图片尺寸1488x525