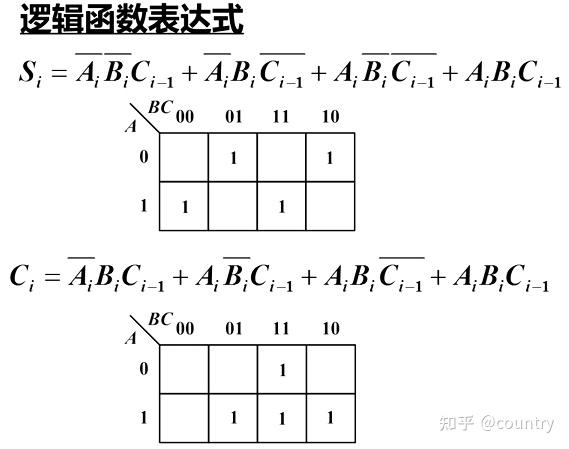

全加器逻辑表达式

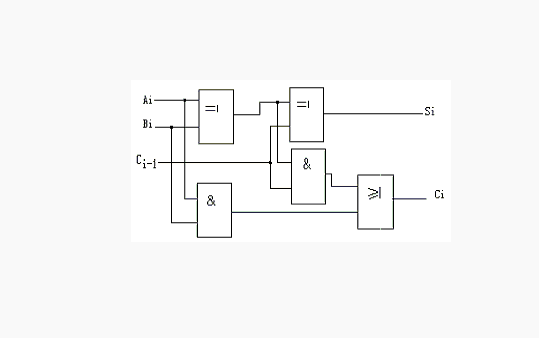

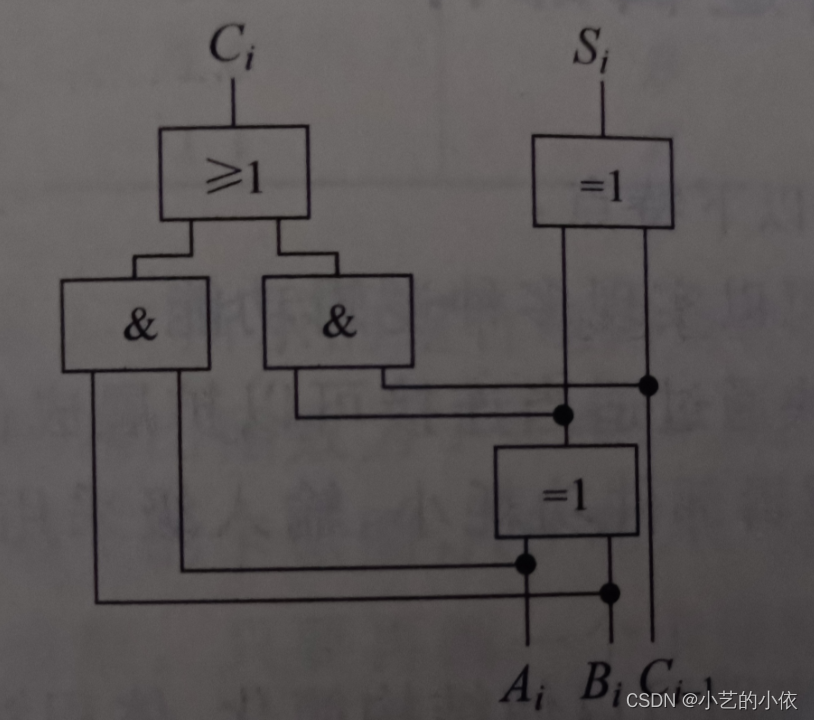

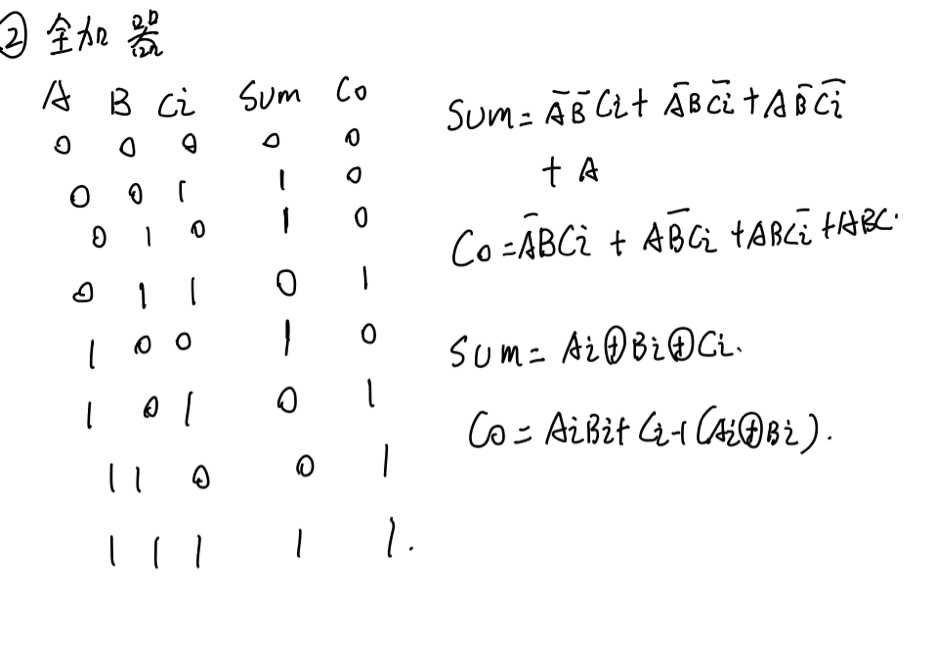

基本思想 一位全加器(fa)的逻辑表达式为: si=ai⊕bi⊕ci ci 1= aibi

图片尺寸1080x810

表中的ai和bi分别表示被加数和加数输入,ci表示来自相邻 低位的进位

图片尺寸1080x810

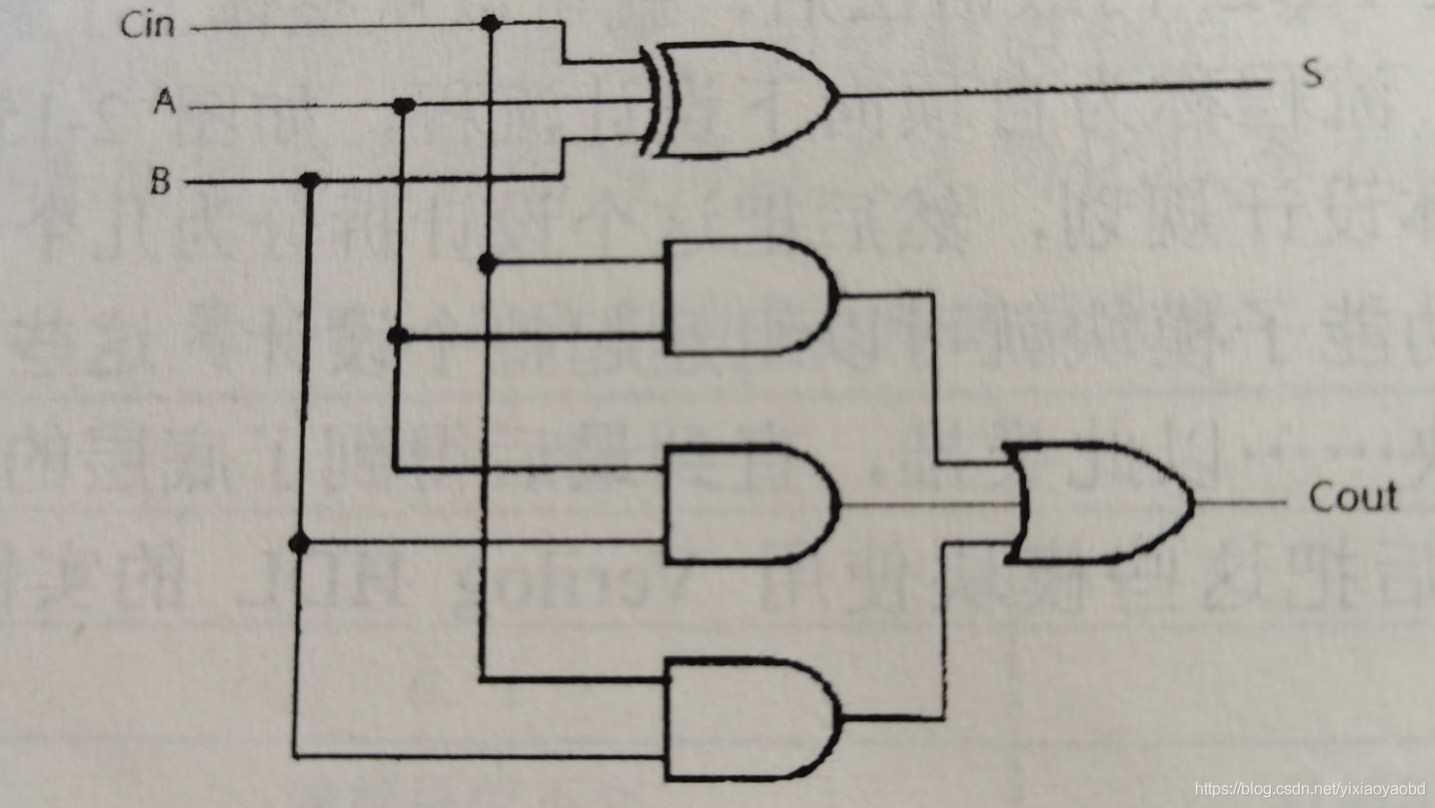

全加器——能同时进行本位数和相邻低位的进位信号的加法运算.

图片尺寸1080x810

3.3全加器

图片尺寸569x449

设计一个数字逻辑中的全加器,要求有实验原理,函数表达式,卡诺图,逻辑

图片尺寸279x224

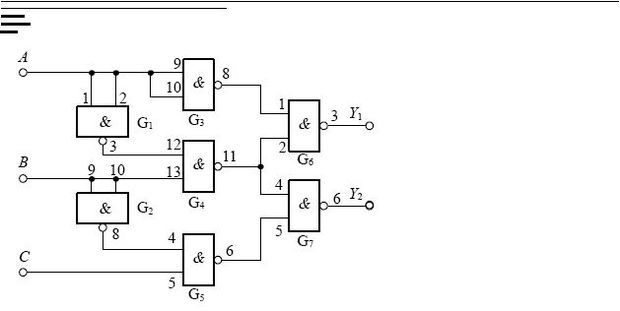

全加器逻辑电路图

图片尺寸620x311

实验五 全加器的应用ppt

图片尺寸1080x810

全加器加法器

图片尺寸802x342

电子/电路 一位全加器实验电路方法的研究 4 种门电路来实现,逻辑电路

图片尺寸353x226

一位二进制全加器

图片尺寸554x328

ppt 数字电路课后习题答案 数字电子技术基础 由真值表写出逻辑表达式

图片尺寸1080x810

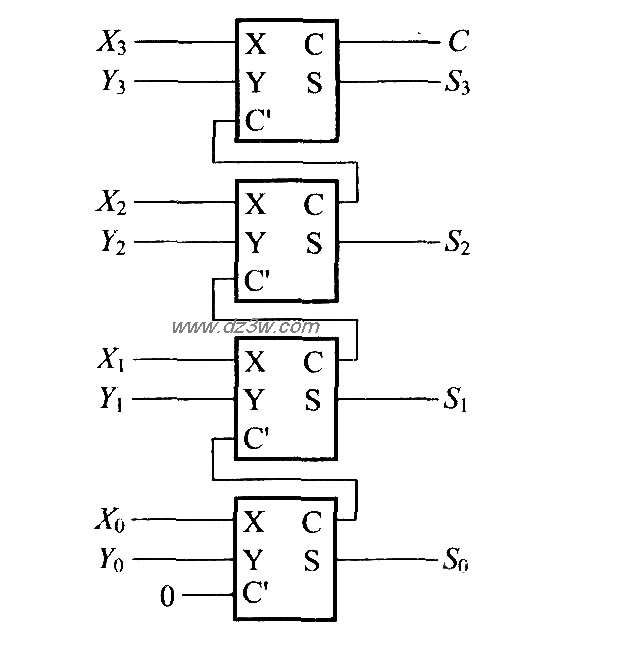

在verilog语言中使用门级建模设计一个由1位全加器组成的4位全加器

图片尺寸1435x808

p>全加器英语名称为full-adder,是用 a href="#" data-lemmaid="

图片尺寸539x338

这个半加器的输出表达式为s=a⊕b,c=ab,逻辑电路图如下一位全加器全加

图片尺寸814x720

全加器

图片尺寸637x649

eda技术讲义 eda技术讲义 全 加 器 被加数,加数以及低位的进位三者

图片尺寸1080x810

verilog8位全加器

图片尺寸936x646

全加器逻辑表达式_全加器的逻辑功能

图片尺寸697x328

(4)将全加器的输出逻辑函数式和数据选择器的输出逻辑函数式进行比较.

图片尺寸564x285

如何用四个全加器构成一个并行进位加法器

图片尺寸600x748