加法器逻辑电路图

数字逻辑课程设计-加法器设计(三位十进制 八位二进制)

图片尺寸1076x796

所示为半加器电路图

图片尺寸609x326

3.加法器仿真电路

图片尺寸743x447

用74283加法器和逻辑门设计实现一位841bcd码加法器电路,输入输出均为

图片尺寸934x429

实验原理 加法器是执行二进制加法运算的逻辑部件,也是cpu运算器的

图片尺寸621x449

逻辑电路图 ③使用全加器元件,设计8位串行进位加法器电路

图片尺寸1424x404

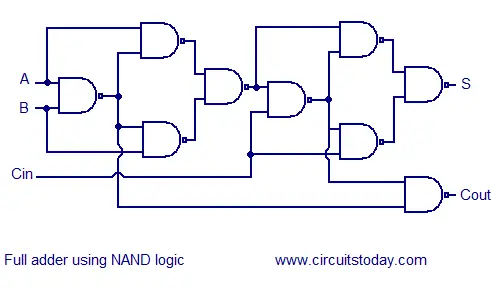

如何只用与非门实现全加器,求逻辑图

图片尺寸926x353

还需要在无符号数加法器的基础上增加相应的逻辑门电路,使加法器不仅

图片尺寸3384x2852

2一位全加器

图片尺寸1105x437

加法器设计--数字逻辑电路(电子科技大学)

图片尺寸621x286

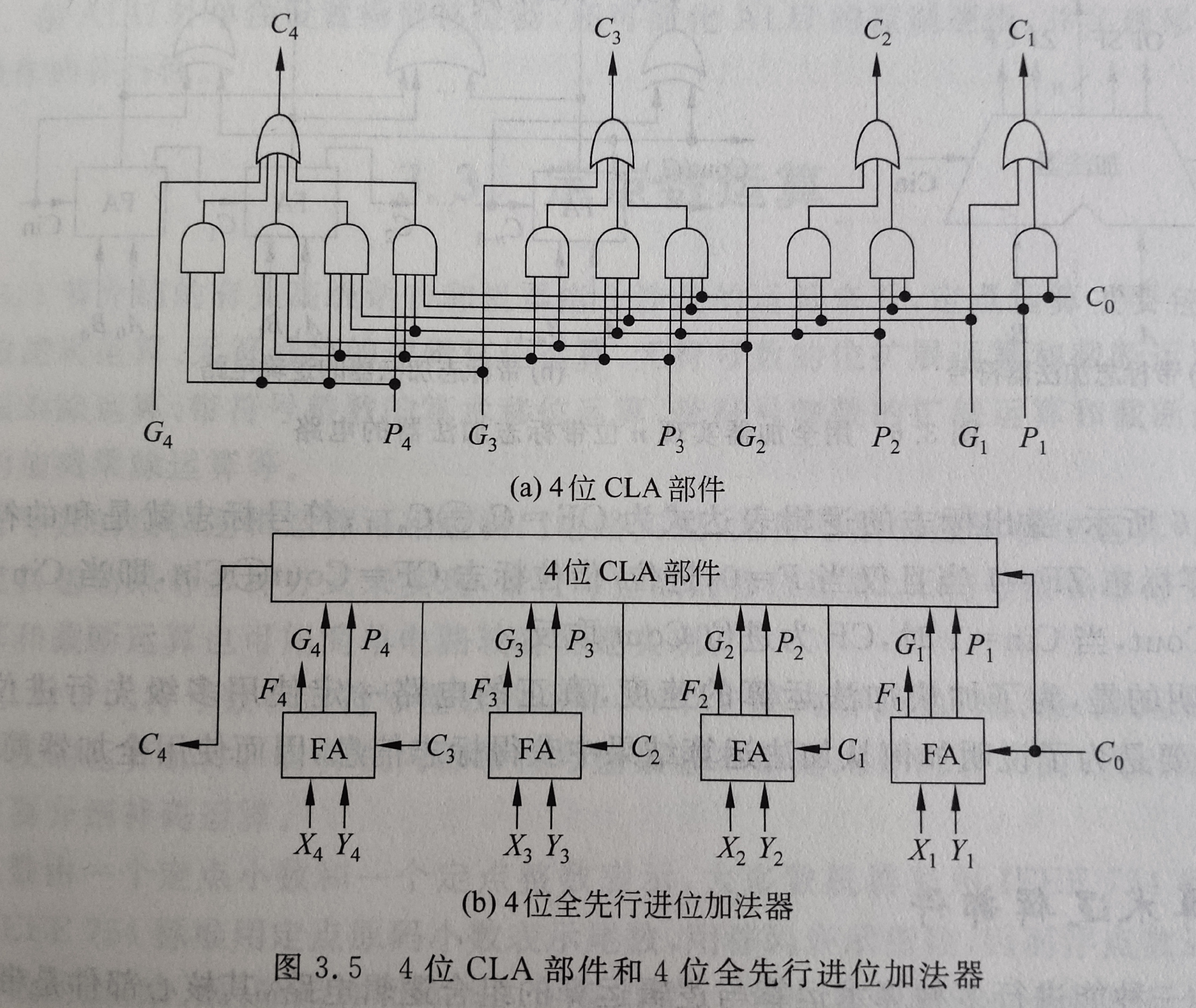

图16 4位超前进位加法器74hc283逻辑图

图片尺寸493x654

用4:1数据选择器实现全加器逻辑功能

图片尺寸425x319

例2逻辑图导出过程图4是用2个4位加法器模块构成8位加法器的逻辑

图片尺寸533x572

四位加法器的逻辑图如下所示

图片尺寸450x302

课题名称组合逻辑全加器.

图片尺寸1820x1412

加法器电路原理二进制加法器原理与非门二进制加法器

图片尺寸456x223

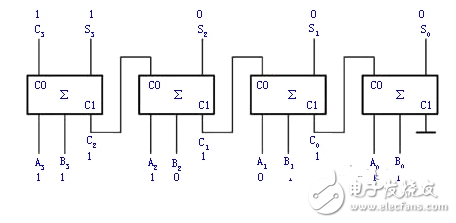

涟波进位加法器

图片尺寸504x294

使用全加器的4位加法运算电路图

图片尺寸600x611

华理数字逻辑实验二全加器

图片尺寸407x317

一位串行bcd加法器电路

图片尺寸500x247