半加器设计

半加器的设计

图片尺寸3000x1875

半加器的设计

图片尺寸876x649

半加器的电路图

图片尺寸826x343

verilog加法器设计

图片尺寸422x261

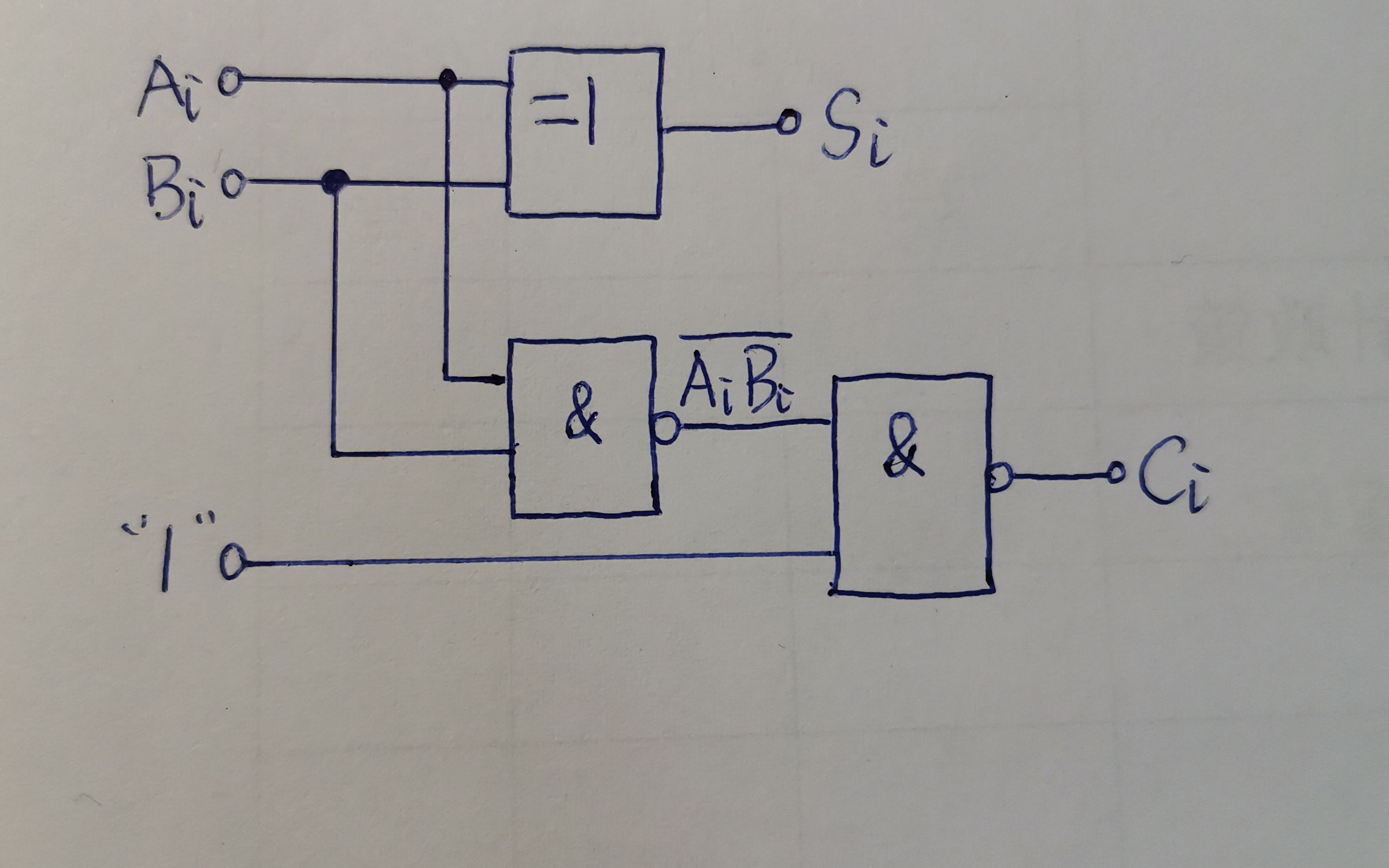

设计一个带控制端的半加/半减器,控制端x=0时为半加器,x=1时为半减器.

图片尺寸710x310

2.1半加器电路的verilog描述 2.1.1半加器的数据流建模描述方式

图片尺寸1082x812

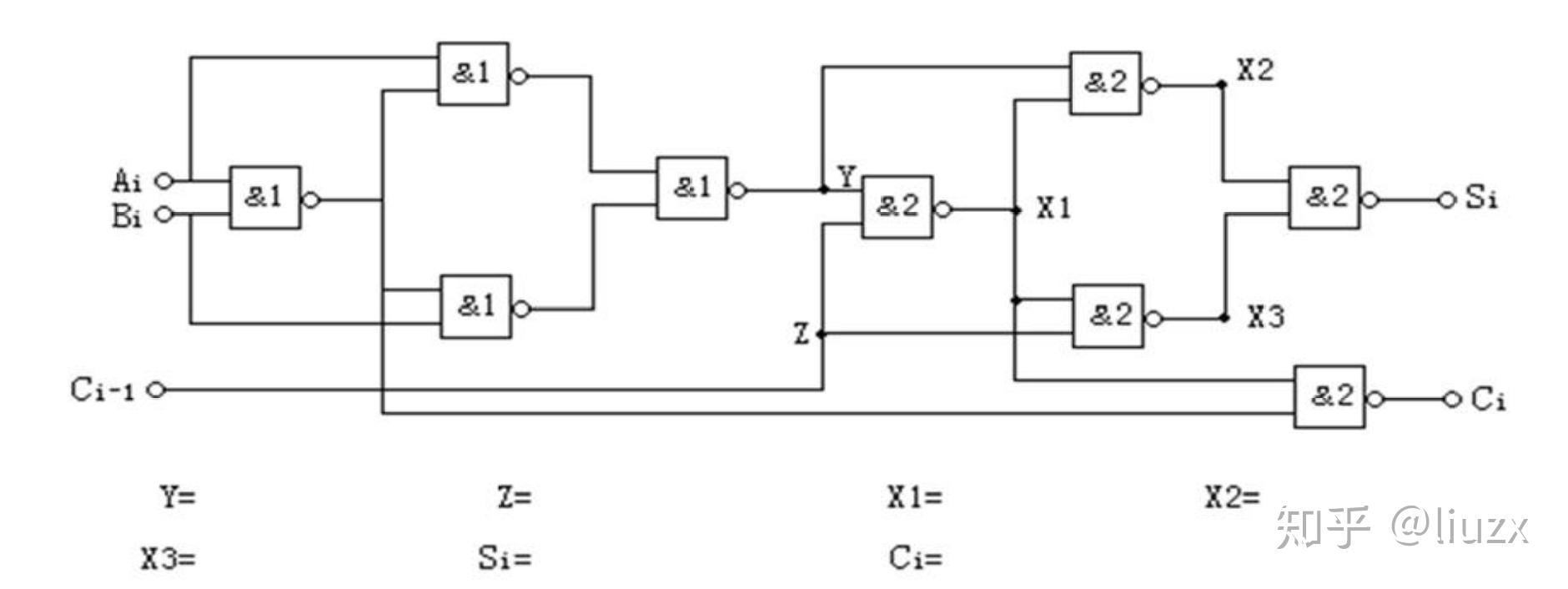

数电实验三全加器应用

图片尺寸1080x697

半加器

图片尺寸1020x346

一,半加器

图片尺寸1156x519

1.半加器(halfadder)

图片尺寸568x420

半加器原理图在quartus ii软件中使用原理图输入法设计并实现一个1位

图片尺寸545x183

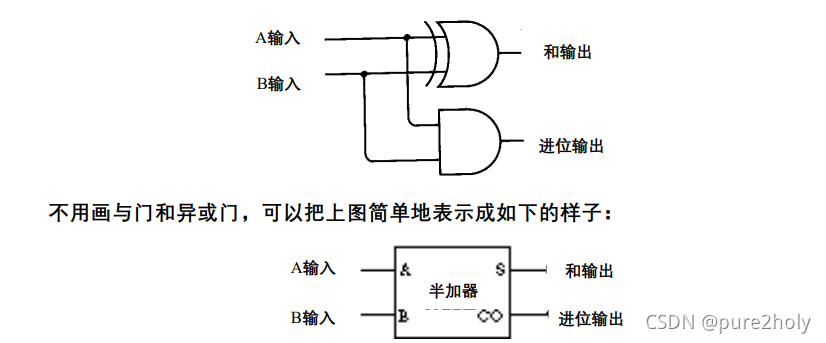

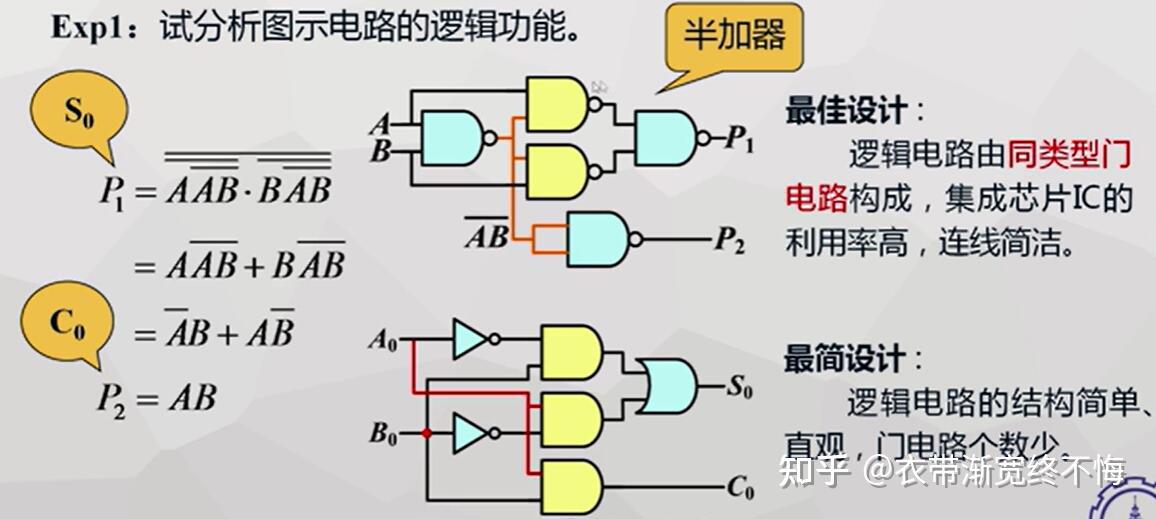

组合逻辑电路设计之全加器半加器

图片尺寸920x1302

组合逻辑电路半加器全加器及逻辑运算实验报告

图片尺寸920x1302

vhdl与数字集成电路设计vhdl41

图片尺寸920x690

半加器,全加器及其应用

图片尺寸399x199

组合逻辑电路半加器全加器及逻辑运算实验报告

图片尺寸920x1303

数电实验 | 组合逻辑电路(半加器全加器及逻辑运算)

图片尺寸1880x706

半加器:2.全加器:3.4位加法器(全加器实现):4.32位加法器的实现:3.

图片尺寸1782x856

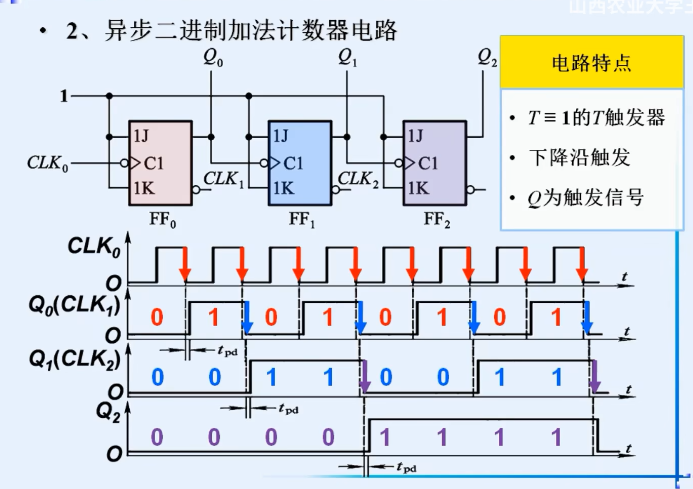

1,异步二进制加法器

图片尺寸693x489

利用全加器构成3位加法计数器( 要有电路图的)

图片尺寸1488x525