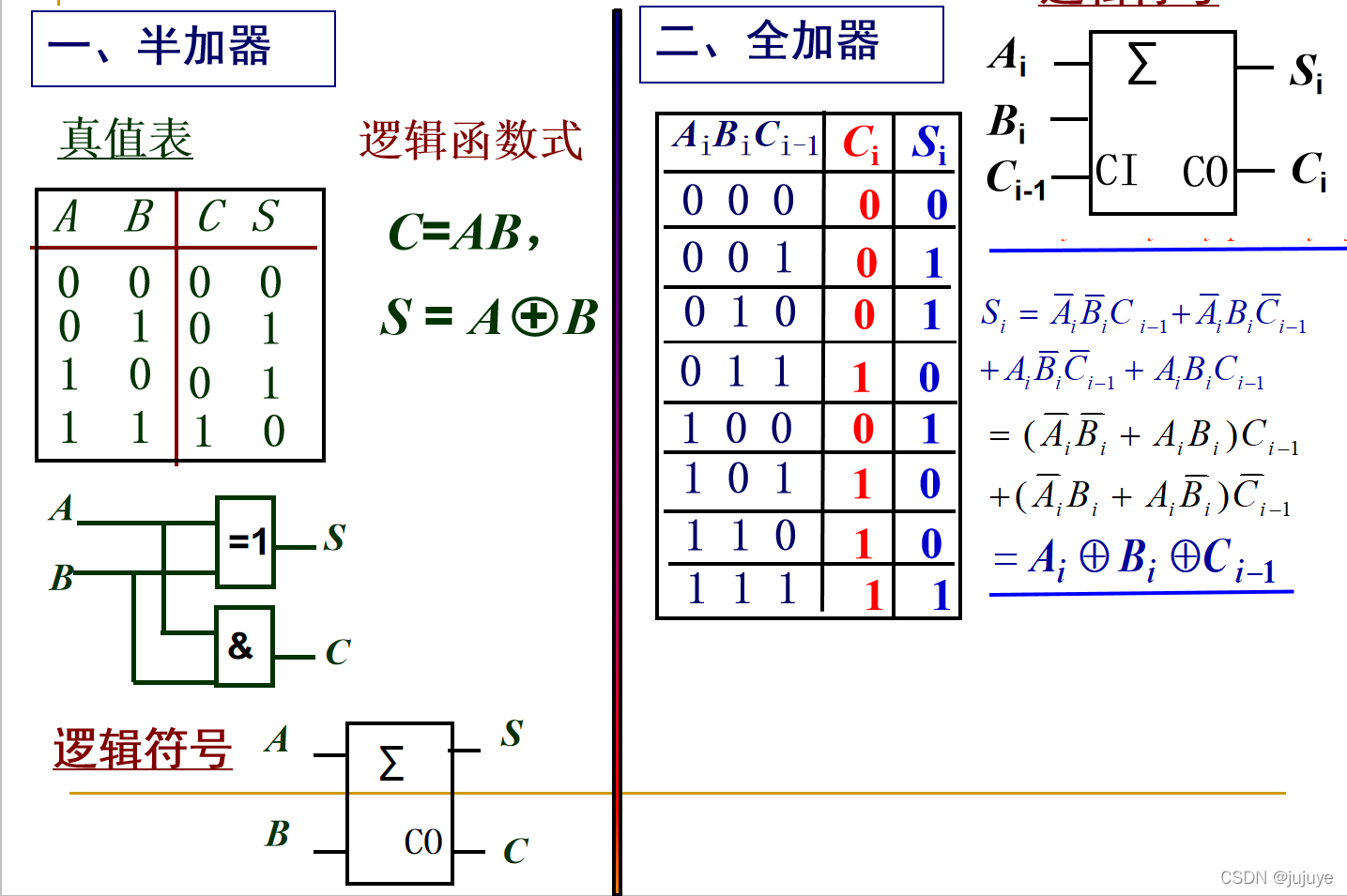

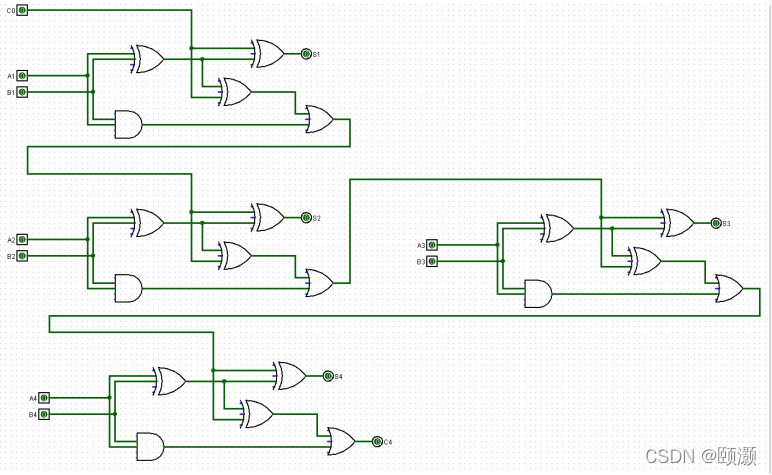

四位全加器逻辑电路图

生成的电路如下所示:我们采用自动生成电路的方法来实现一位全加器:1

图片尺寸2160x1440

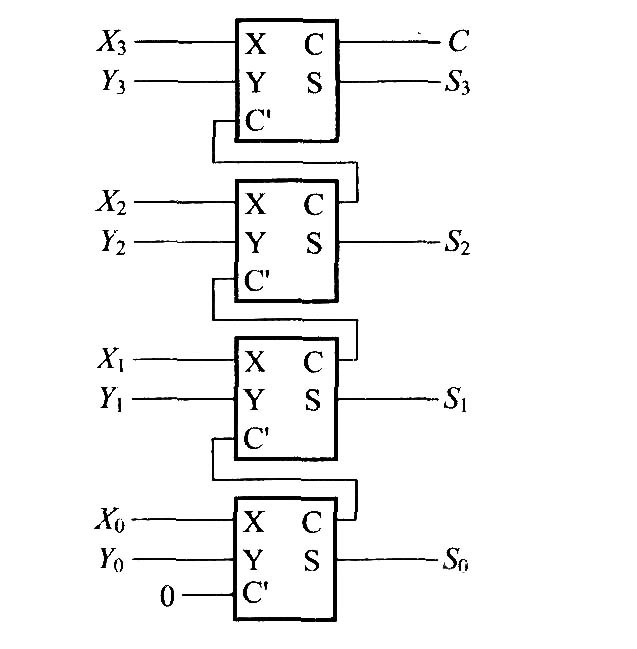

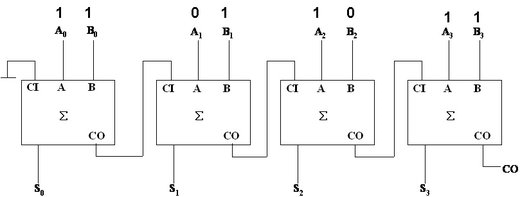

使用全加器的4位加法运算电路

图片尺寸637x649

使用全加器的4位加法运算电路图

图片尺寸600x611

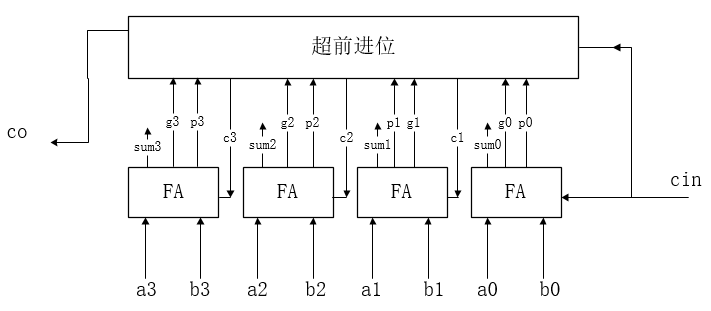

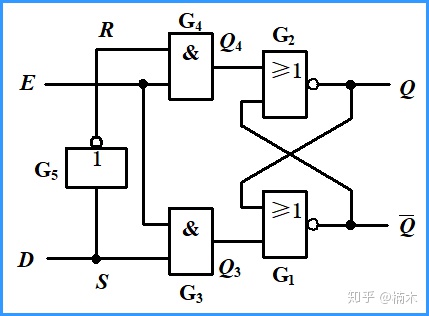

带超前进位的四位全加器

图片尺寸492x555

quartusii四位加法器设计图计组课设

图片尺寸913x420

基于verilog hdl的超前进位全加器设计

图片尺寸711x311

四位加法器的电路图

图片尺寸920x1302

超级全加器的4位加法运算电路图

图片尺寸400x408

试用四位集成全加器实现将余3bcd码转换为8421bcd码的电路.

图片尺寸466x247

下图所示为2个4位二进制数相加的串接全加器逻辑电路图运算后的cos3s2

图片尺寸520x197

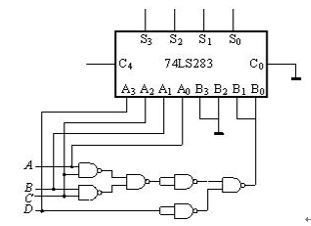

由四位并行进位全加器74ls283构成图所示

图片尺寸486x378

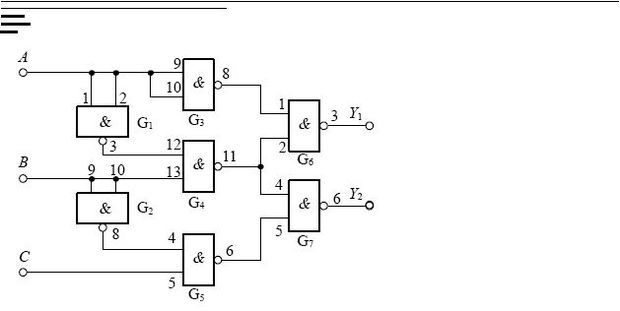

全加器逻辑电路图

图片尺寸620x311

用集成四位全加器74ls283和二输入与非门构成电路如图所示输入为bcd

图片尺寸311x226

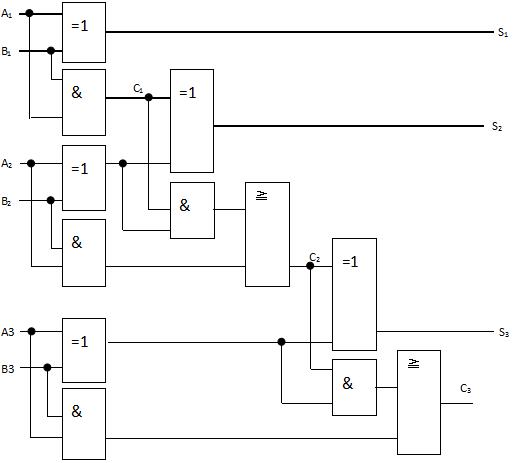

4位并行加法器

图片尺寸341x254

四位全加器余三码转8421码逻辑电路图 - csdn

图片尺寸646x563

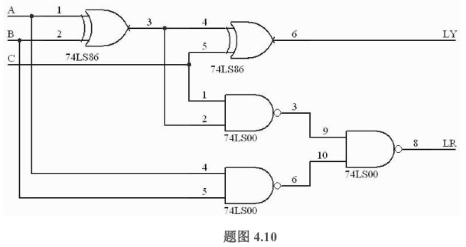

采用逻辑处理方法实现加法运算的数字电路.

图片尺寸1435x955

如何用四个全加器构成4位并行进位加法器

图片尺寸600x400

四位全加器余三码转8421码逻辑电路图 - csdn

图片尺寸429x316

以下是本篇文章正文内容,下面案例可供参考二,四位并行加法器(1)逻辑

图片尺寸772x475

器真值表列表,真值表在电路设计时非常重要,在逻辑表达和电路分析时能

图片尺寸527x463