设计半加器

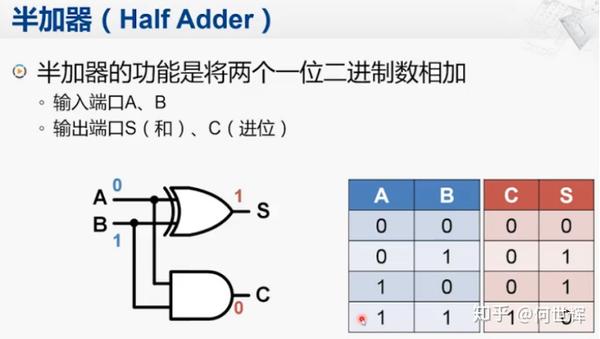

半加器的设计

图片尺寸3000x1875

半加器的设计

图片尺寸876x649

下面电路中,能实现半加器功能的是 .

图片尺寸424x349

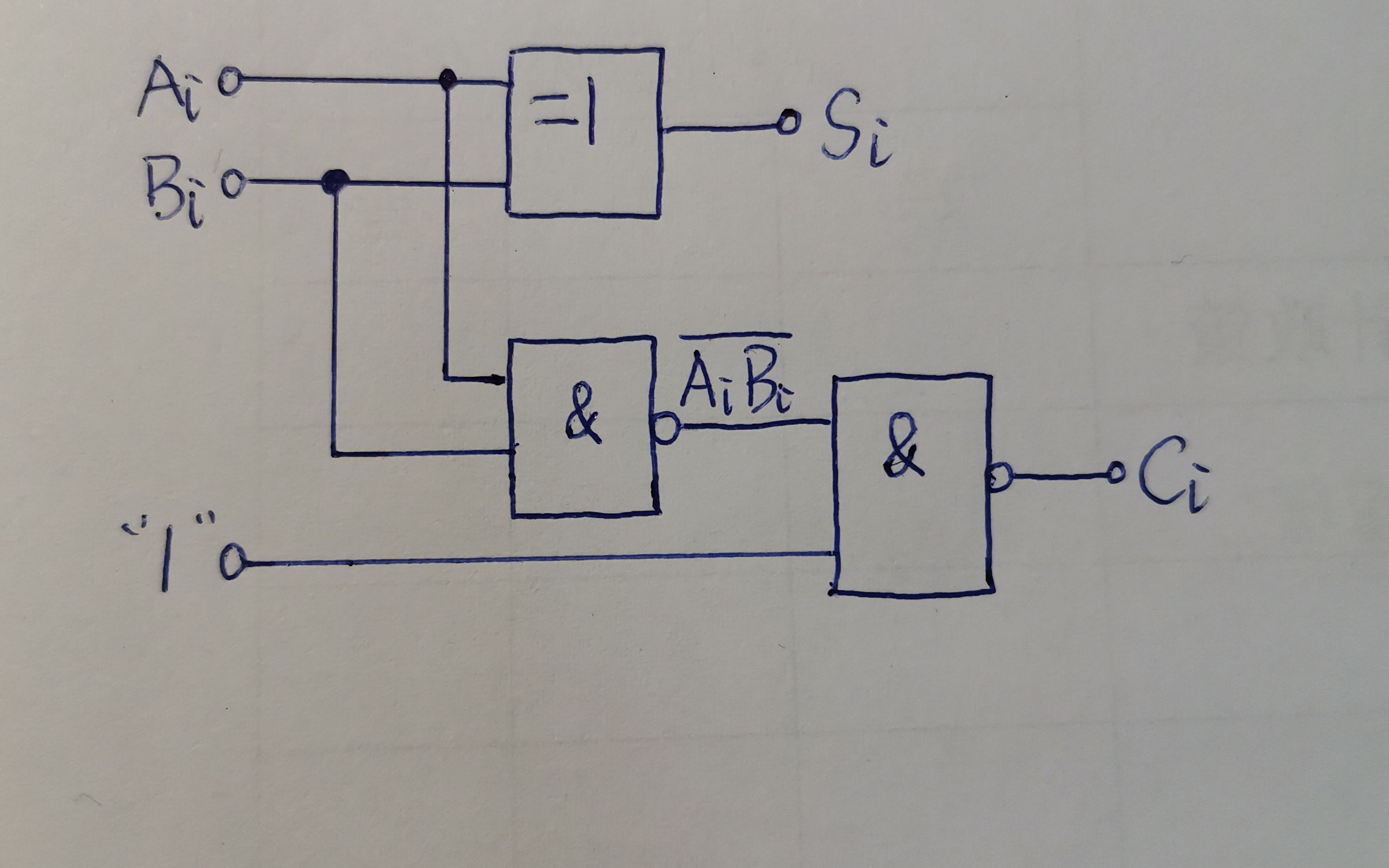

设计一个带控制端的半加/半减器,控制端x=0时为半加器,x=1时为半减器.

图片尺寸710x310

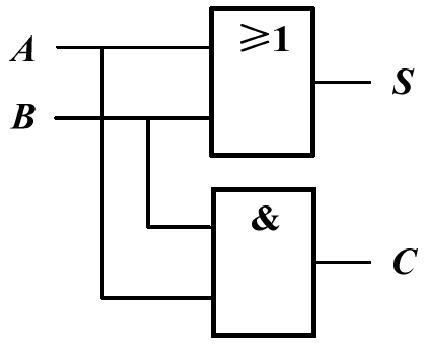

所示为半加器电路图

图片尺寸609x326

verilog加法器设计

图片尺寸422x261

第1关:半加器设计

图片尺寸1370x660

半加器的电路图

图片尺寸826x343

2.1半加器电路的verilog描述 2.1.1半加器的数据流建模描述方式

图片尺寸1082x812

半加器的设计

图片尺寸1400x682

怎样用半加器和或门组成全加器 还有电路图

图片尺寸500x314

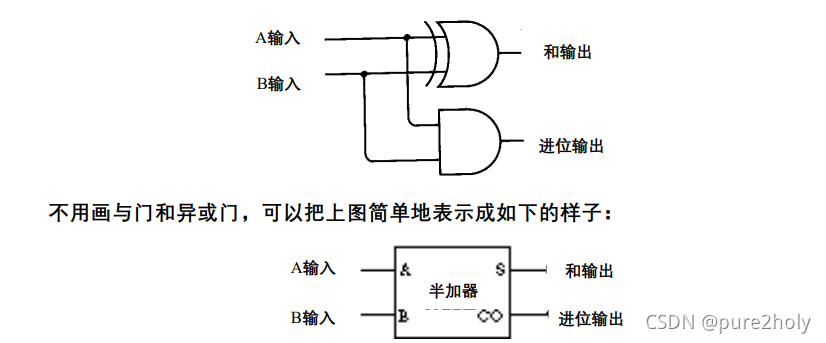

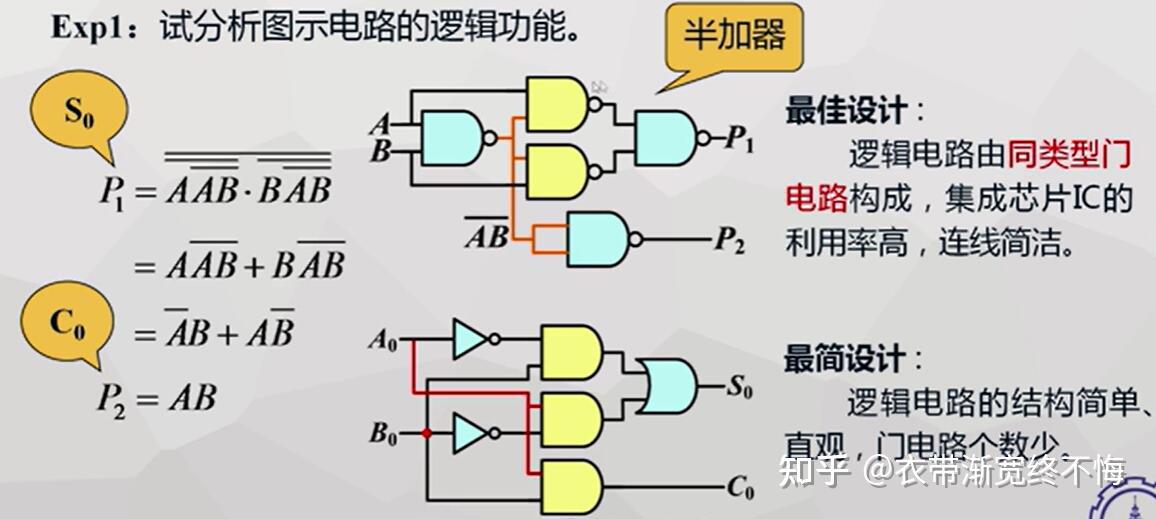

组合逻辑电路设计之全加器半加器

图片尺寸920x1302

一,半加器

图片尺寸1156x519

半加器和全加器的区别在于半加器无进位输出_用半加器设计全加器的

图片尺寸421x315

《数字逻辑课程设计-加法器设计(三位十进制 八位二进制)》

图片尺寸1076x796

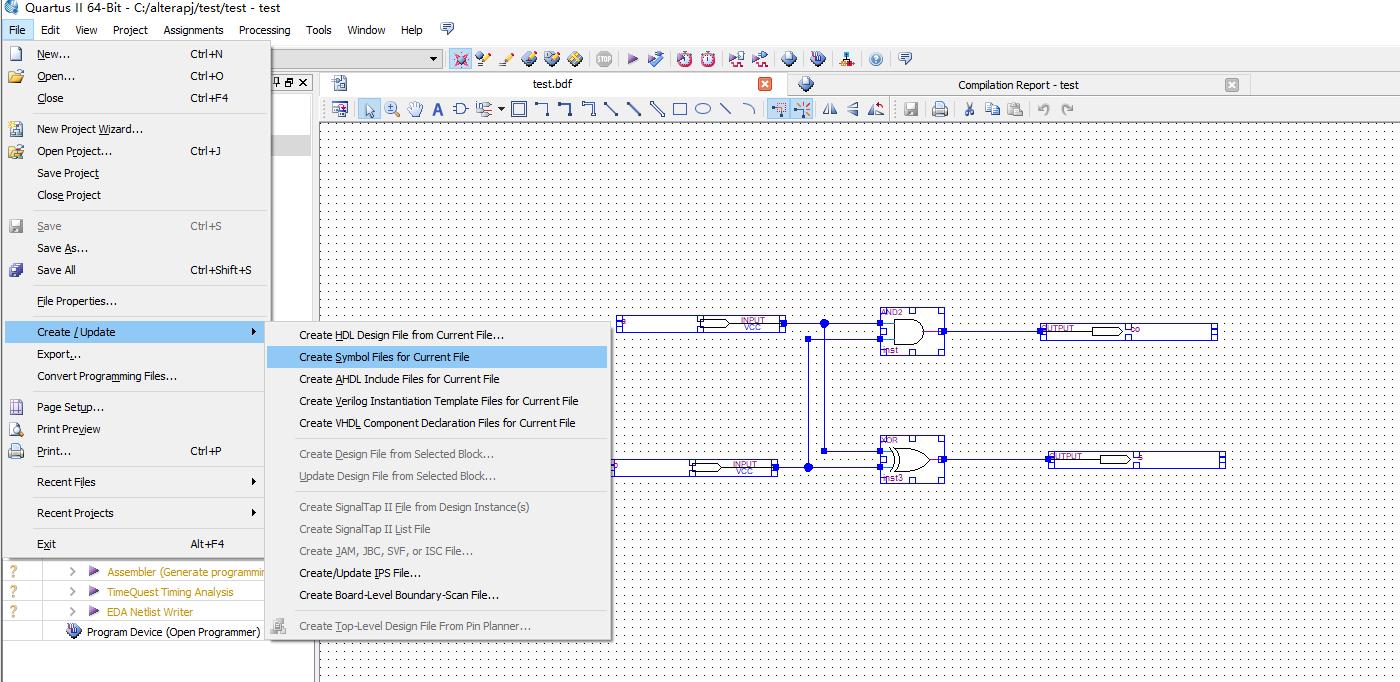

半加器原理图在quartus ii软件中使用原理图输入法设计并实现一个1位

图片尺寸545x183

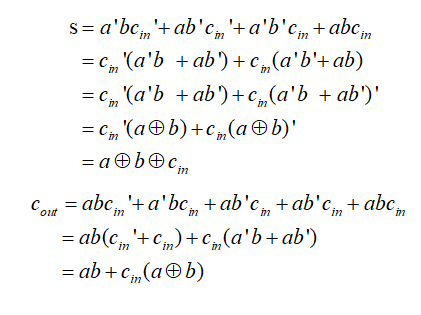

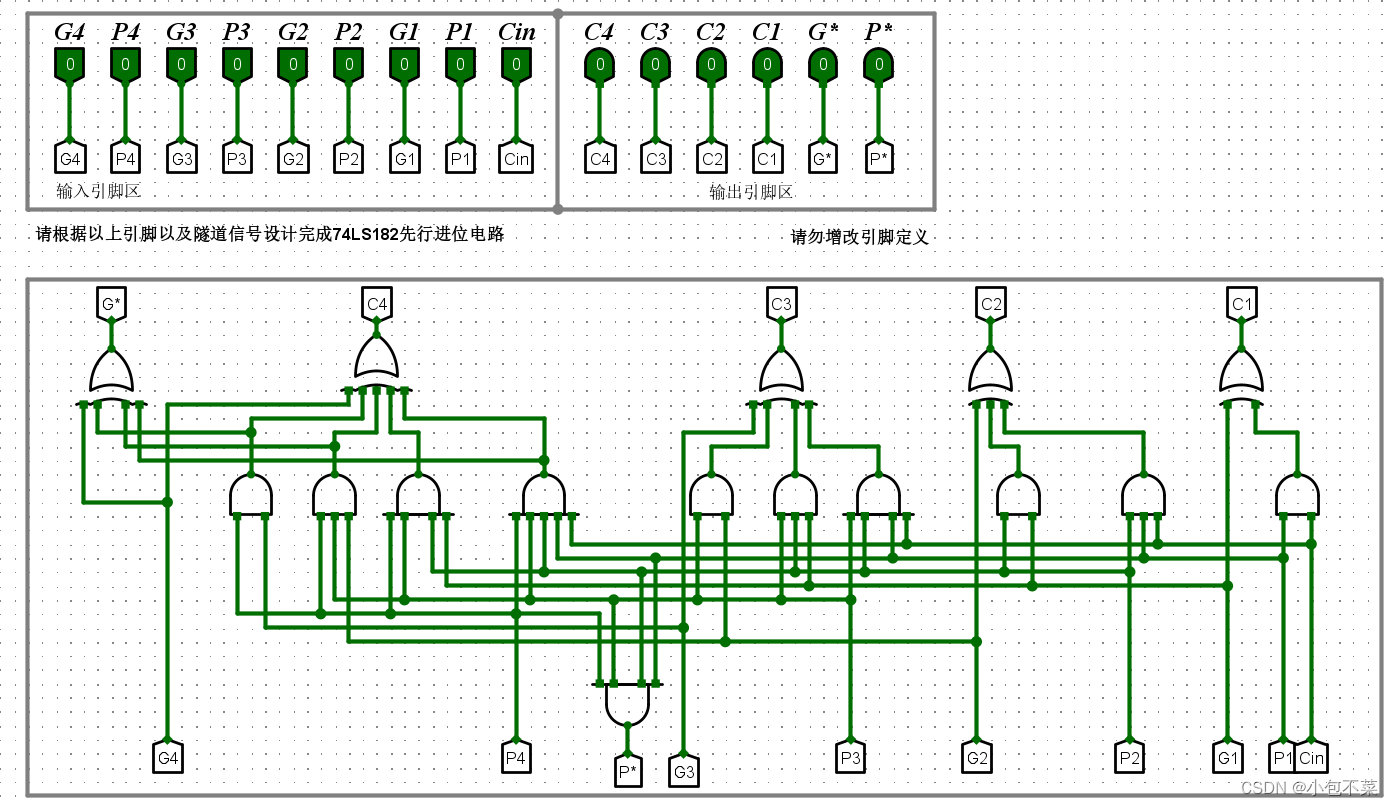

2.快速加法器的设计

图片尺寸1393x806

构建一个加法器

图片尺寸1386x830

16位加法器设计_第1页

图片尺寸1649x2303

5 天前 · 来自专栏 硬件电路设计 1,先了解下什么是半加器 2,什么是

图片尺寸693x391