38译码器逻辑图

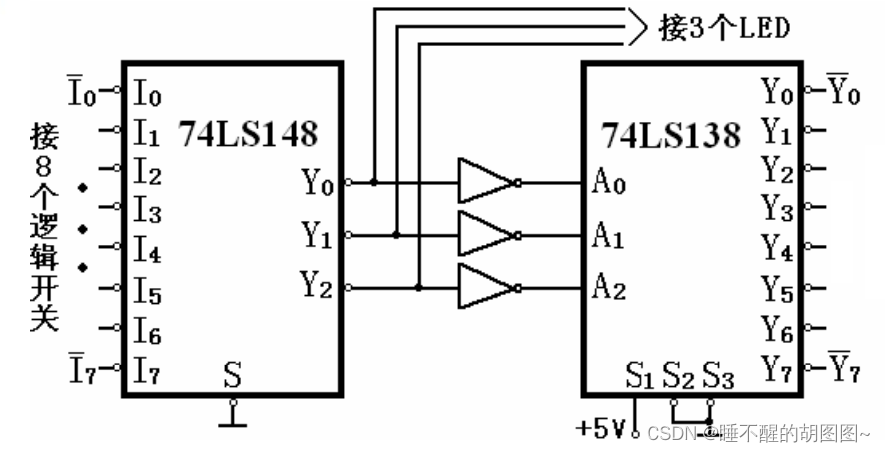

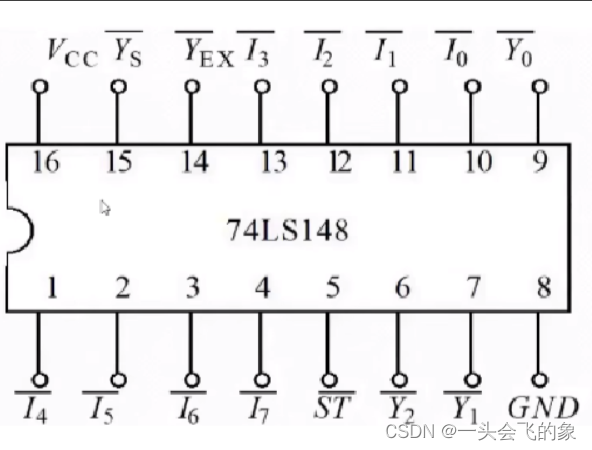

2.三八译码器

图片尺寸1232x542

2.三八译码器

图片尺寸418x327

2.三八译码器

图片尺寸1166x752

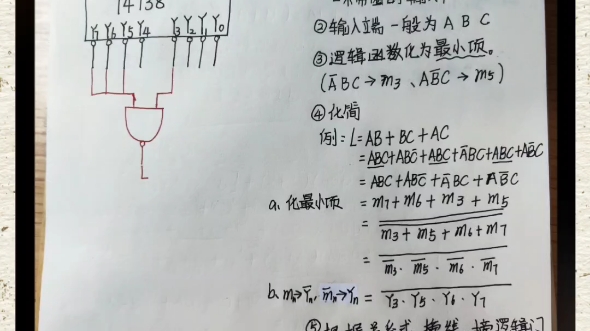

38译码器实现逻辑电路

图片尺寸1080x810

一张图学会儿74138译码器

图片尺寸590x331

① 先画出3-8译码器的逻辑图

图片尺寸451x312

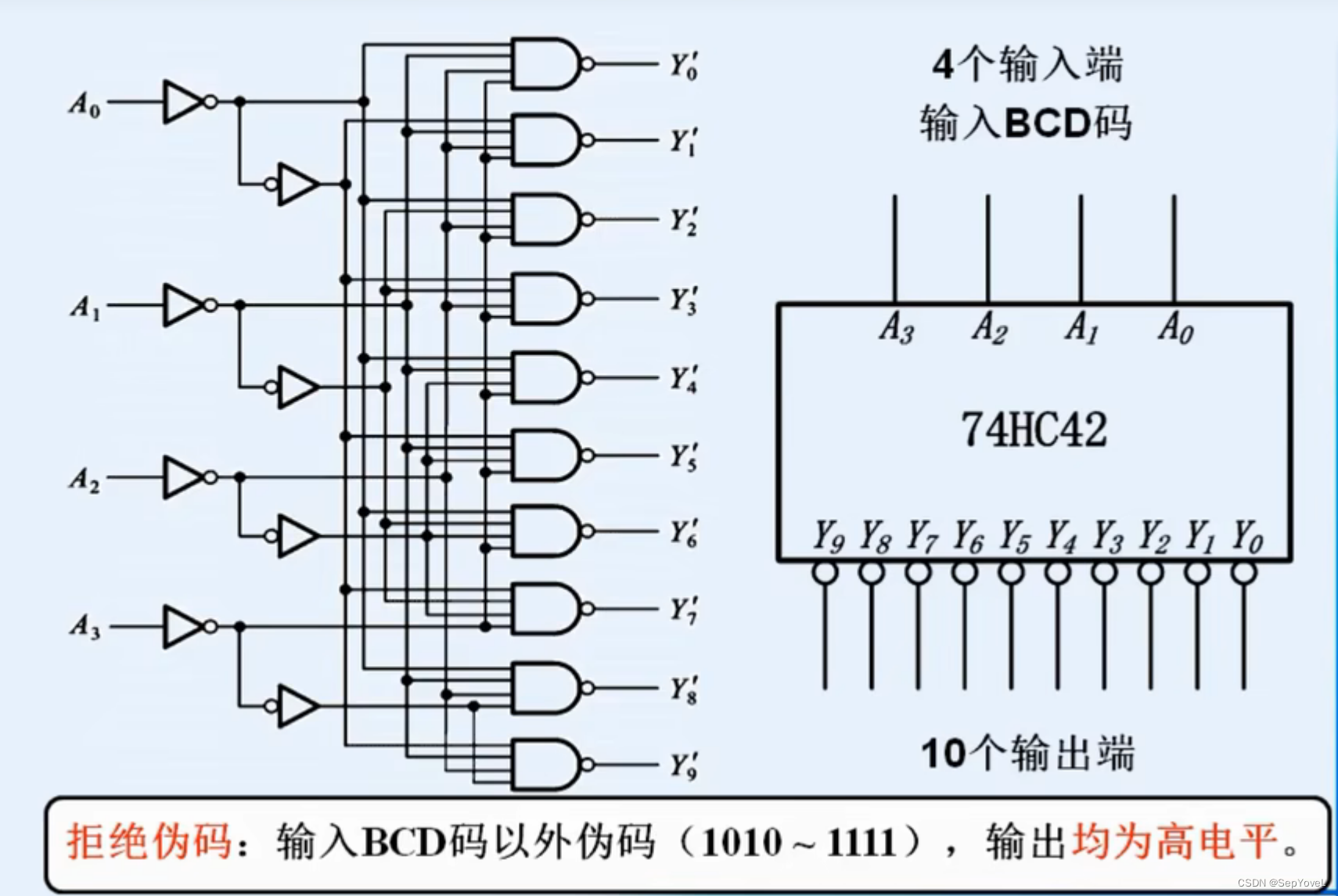

数字逻辑电路学习期末复习组合逻辑电路常用器件

图片尺寸1710x1145

上图为常用的集成译码器74138,其功能表为: 由逻辑图可知,该译码器

图片尺寸326x327

38译码器实现逻辑电路

图片尺寸920x690

并转换成控制信号,具有译码功能的逻辑电路称为译码器

图片尺寸871x430

编码器与解码器原理编码器的逻辑功能是将2的n次方个输入信号的高/低

图片尺寸949x1462

编码器的定义:编码器(encoder)的逻辑功能是将2的n次方个输入信号的高

图片尺寸1018x759

3-8译码器的逻辑线路图如图所示在本实验中,采用原理图设计方法实现一

图片尺寸1005x512

由38译码器74ls138和逻辑门构成的组合逻辑电路如图p416所示1试分别

图片尺寸302x275

编码器与解码器原理编码器的逻辑功能是将2的n次方个输入信号的高/低

图片尺寸885x452

用74138译码器扩展成5/32译码电路

图片尺寸600x436

编码器与解码器原理编码器的逻辑功能是将2的n次方个输入信号的高/低

图片尺寸566x595

数字电路逻辑设计总结

图片尺寸774x520

编码器的定义:编码器(encoder)的逻辑功能是将2的n次方个输入信号的高

图片尺寸592x450

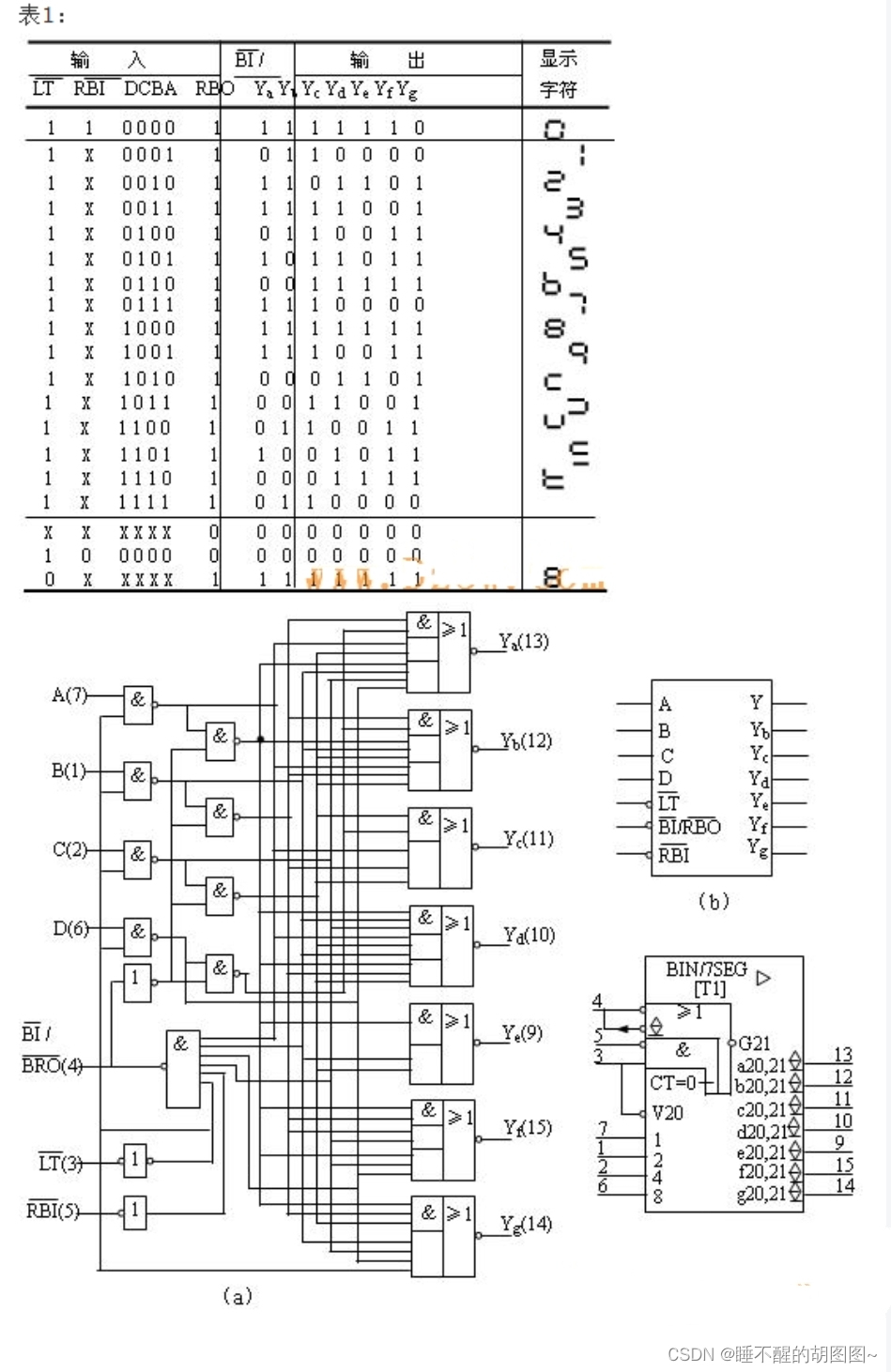

如下图所示:bcd-七段显示译码器7448的

图片尺寸447x524

1.jpg)