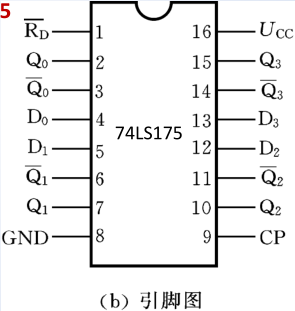

74ls175引脚图及原理

由图1(a)可知,寄存器74ls175由4个下降沿触发的边沿d触发器组成,4个d

图片尺寸272x270

【数字逻辑】学习笔记 第五章 part3 时序逻辑电路

图片尺寸295x311

74ls00与74ls10引脚图

图片尺寸893x288

双d触发器74ls74

图片尺寸1213x884

1,引脚图2,真值表3,工作原理1s,2s为选通端,低电平有效.

图片尺寸638x458

(2)74ls74引脚图

图片尺寸893x228

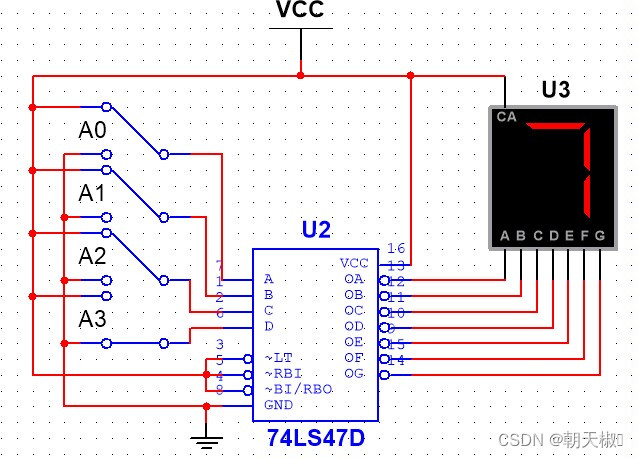

> 动态扫描显示电路实验的设计与实现实际电路可选择1片74ls175(四d

图片尺寸827x437

用数据选择器74ls153实现接线图

图片尺寸1080x810

3 若干常用的时序逻辑电路(寄存器)ppt 二,集成寄存器74ls175 q0 q0

图片尺寸1080x810

潮流上机实验.pptx

图片尺寸1152x864

过程: 板书或旁注 (3)数值比较器的位数扩展 串联方式 用 2 片 7485

图片尺寸709x1030

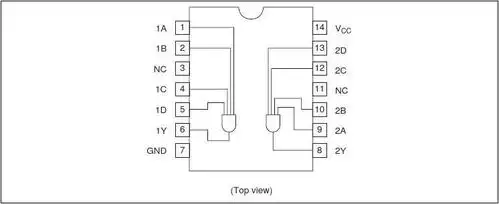

dm74ls75mx中文资料

图片尺寸769x652

下面介绍一下常用的74芯片,以便大家在电路中遇到了查询

图片尺寸554x79974ls283引脚图及相关功能介绍!

图片尺寸640x340

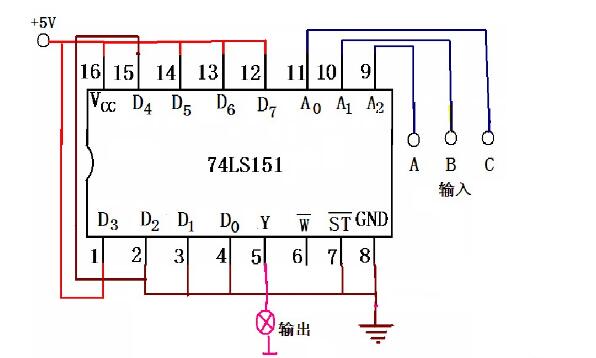

74ls151中文资料汇总(74ls151引脚图及功能_工作原理及应用电路)-电子

图片尺寸596x358

74ls175的引脚及逻辑符号图

图片尺寸495x256

74系列数字电路7417574ls175四d型触发器带清除端

图片尺寸1445x1578

hd74ls21p中文资料

图片尺寸746x305

图6-190 74ls48 共阴4-7译码器/驱动器图6-189 74ls47 共阳4-7译码器

图片尺寸815x622

四路智能抢答器(自己设计的)

图片尺寸660x617

猜你喜欢:74ls00引脚图及功能74ls192引脚图及功能74ls20引脚图74ls0074ls20引脚图及功能cd4012芯片引脚图74ls175引脚图及真值表74ls17574ls175引脚图及功能74ls161引脚图及功能74ls175引脚图及功能表74ls175引脚图74ls161引脚图74ls148引脚图74hc175引脚图及功能74ls160引脚图74ls138引脚图74ls04引脚图及功能表74ls20引脚图及真值表74ls192引脚图及真值表74ls192引脚图74ls86引脚图及功能74ls47引脚图74ls04引脚图74ls175管脚图74ls32引脚图及功能表74LS20引脚图及功能lm324引脚图及功能cd4511引脚图lm317引脚图贴符搞笑图片喝酒前后对比搞笑图片转账200的图片微信铅笔盒怎么画打架子鼓gifZ50次早日康复表情包认错哄女朋友的表情包热市镇温德姆酒店奔奔解说本人照片曝光西京医院住院24节气国画