四位加法器逻辑图

带超前进位的四位全加器

图片尺寸492x555

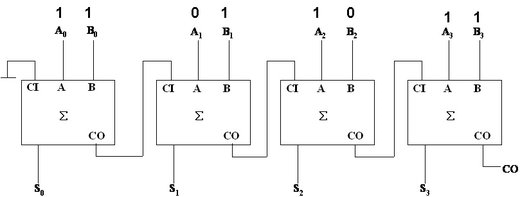

下图所示为2个4位二进制数相加的串接全加器逻辑电路图运算后的cos3s2

图片尺寸520x197

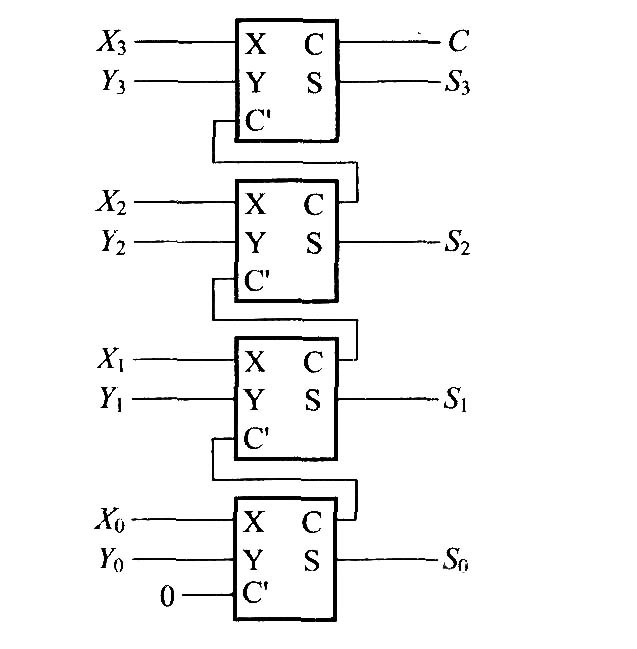

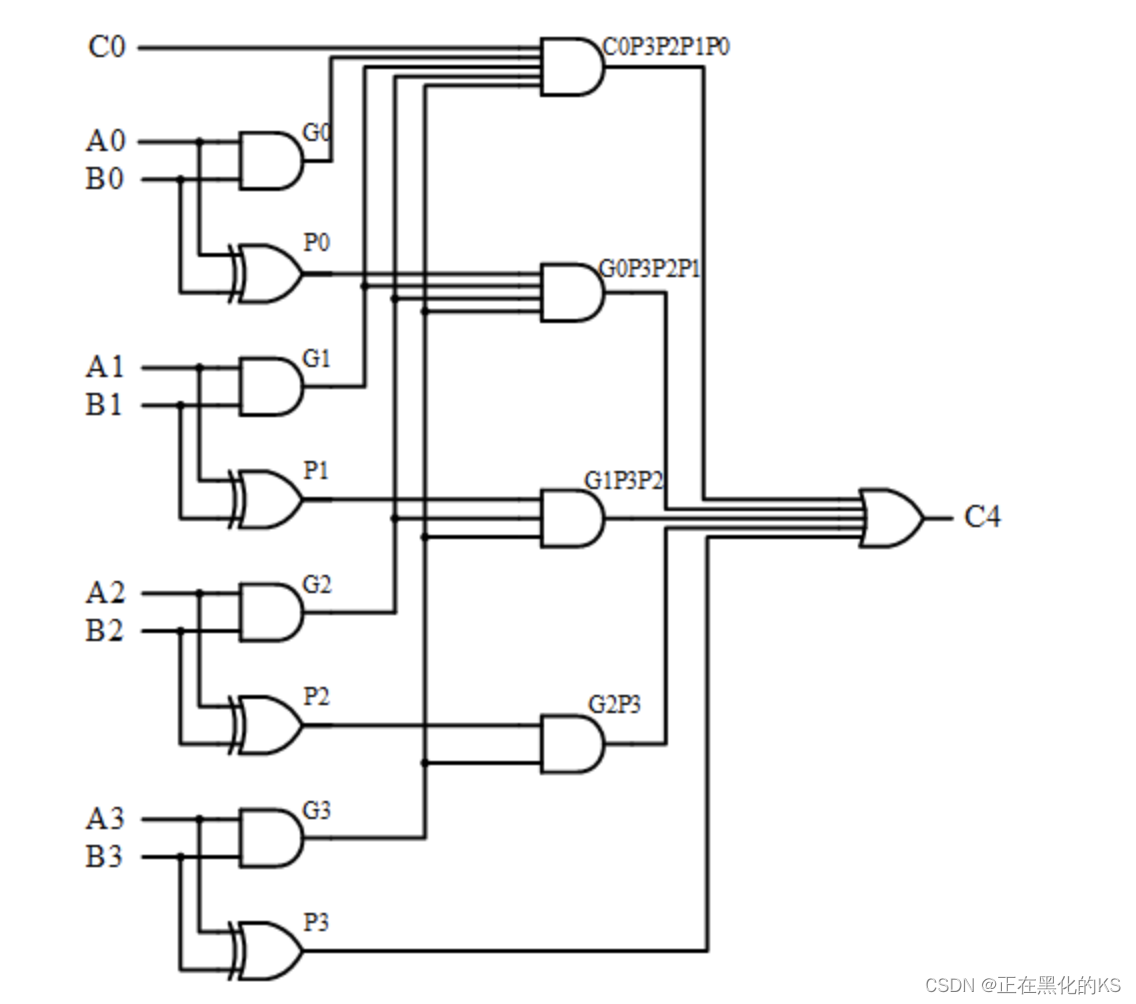

四位前进位加法器设计

图片尺寸617x474

四位加法器的逻辑图如下所示

图片尺寸450x302

使用全加器的4位加法运算电路

图片尺寸637x649

使用全加器的4位加法运算电路图

图片尺寸600x611

4位并行加法器

图片尺寸341x254

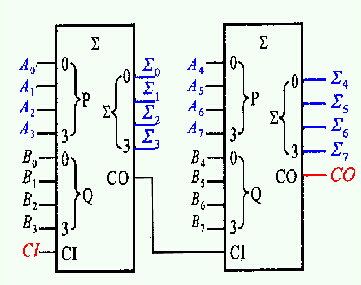

例2逻辑图导出过程图4是用2个4位加法器模块构成8位加法器的逻辑

图片尺寸533x572

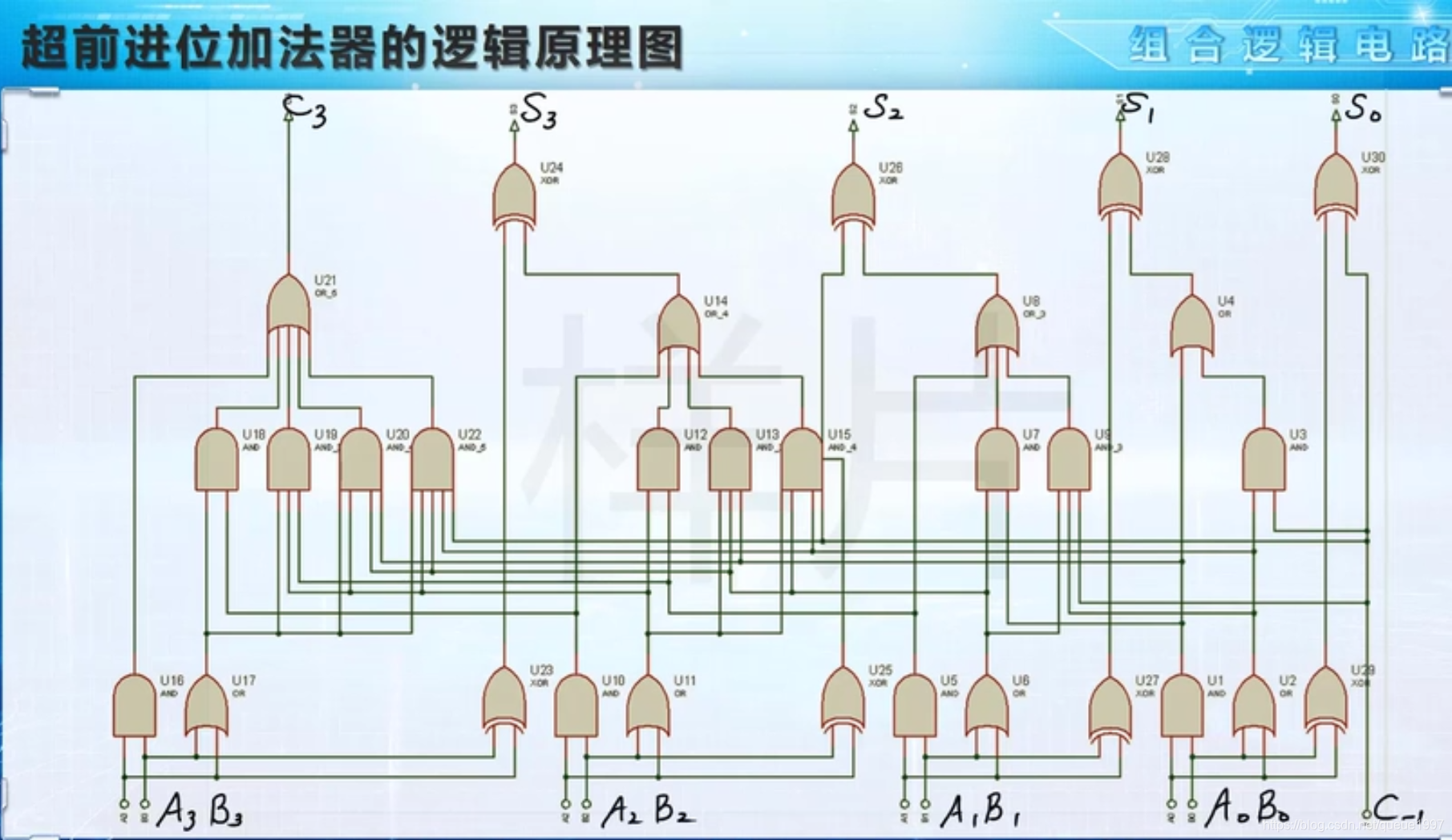

4位超前进位加法器设计

图片尺寸1159x581

使用全加器的4位加法运算电路图

图片尺寸600x611

超级全加器的4位加法运算电路图

图片尺寸400x408

4位并行加法器

图片尺寸361x285

logisim实现4位加法器

图片尺寸673x603

计算机组成实验四位加法器

图片尺寸1811x1048

19 利用4位集成加法器74ls283和适当的逻辑门电路,实现一位余3代码的

图片尺寸490x288

使用74283搭建的四位二进制加法器

图片尺寸1190x658

4位的加法运算减法运算电路

图片尺寸705x741

verilog学习笔记4bit超前进位加法器电路

图片尺寸1136x1004

用4位加法器74ls283和4位2选1数据选择器74ls157设计一个可控码组转换

图片尺寸294x237

四位加法器的电路图

图片尺寸920x1302

猜你喜欢:四位加法器四位全加器四位全加器真值表四位加法器电路图二位加法器逻辑图加法器逻辑电路图四位加法器原理图四位加法器真值表4位加法器电路图加法器图片加法器波形图八位加法器4位加法器多位加法器加法器仿真图全加器逻辑电路图一位全加器逻辑电路图加法器电路图半加器逻辑电路图八位加法器电路原理图简单加法器电路图加法器仿真电路图加法器加法器原理及电路图二进制加法器电路图加法器芯片加法器实验电路连接图加法器电路机械加法器4bit加法器电路图流星雨视频素材情侣头像 微信 壁纸北面腰果花棉服蓝色艾莎的冰雪城堡图片夕立poi 壁纸天地粮人人物大结局最丑的老婆子照片蹀躞怎么读永乐古窖董事长菖蒲图片大全功效人机料法环ppt素材乌尼莫克房车多少钱

1.jpg)